**Tutorial 16**

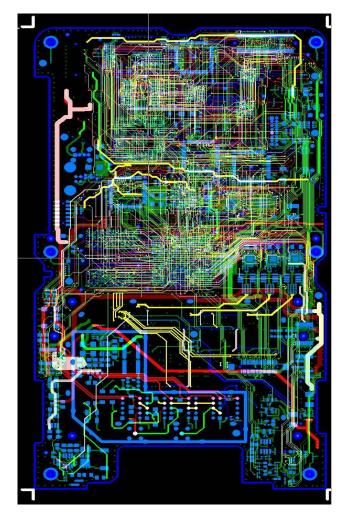

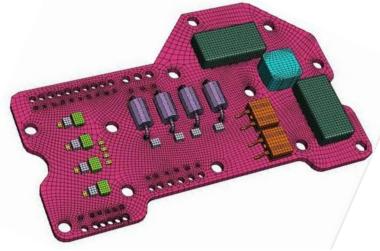

### Design for Reliability & Sourcing of Printed Circuit Boards

Cheryl Tulkoff Senior Member of the Technical Staff ctulkoff@dfrsolutions.com

Dr. Viktor Tiederle President Reliability Technology Viktor.Tiederle@RELNETyX.com

### **DfR Course Abstract**

Designing printed boards and assemblies today is more difficult than ever before because of the increased lead free process temperature requirements and associated changes required in manufacturing. Not only has the density of the electronic assembly increased, but many changes are taking place throughout the entire supply chain regarding the use of hazardous materials and the requirements for recycling. Much of the change is due to the European Union (EU) Directives regarding these issues. The RoHS and REACH directives have caused many suppliers to the industry to rethink their materials and processes. Thus, everyone designing or producing electronics has been or will be affected.

### Instructor 1 Biography

- Cheryl Tulkoff has over 22 years of experience in electronics manufacturing with an emphasis on failure analysis and reliability. She has worked throughout the electronics manufacturing life cycle beginning with semiconductor fabrication processes, into printed circuit board fabrication and assembly, through functional and reliability testing, and culminating in the analysis and evaluation of field returns. She has also managed no clean and RoHS-compliant conversion programs and has developed and managed comprehensive reliability programs.

- Cheryl earned her Bachelor of Mechanical Engineering degree from Georgia Tech. She is a

published author, experienced public speaker and trainer and a Senior member of both ASQ

and IEEE. She holds leadership positions in the IEEE Central Texas Chapter, IEEE WIE

(Women In Engineering), and IEEE ASTR (Accelerated Stress Testing and Reliability)

sections. She chaired the annual IEEE ASTR workshop for four years and is also an ASQ

Certified Reliability Engineer.

- She has a strong passion for pre-college STEM (Science, Technology, Engineering, and Math) outreach and volunteers with several organizations that specialize in encouraging pre-college students to pursue careers in these fields.

### Instructor 2 Biography

- Dr. Viktor Tiederle has over 29 years of experience in interconnection technology for microelectronic devices. He has worked in nearly all areas from development to production with the emphasis on quality and reliability. He started with his work in thick film technology and soldering techniques in SMD ceramics in the early 1980's. Later we worked in wire bonding technique as well as in adhesive technology and developing micromechanical devices for automotive applications. Since more than 10 years he is responsible for many projects within the automotive as well as other industrial segments, for example in photovoltaic.

- Viktor earned his Diploma of Physics at the Technical University of Munich and Stuttgart. After some years of industrial work he received his Dr.-Eng. degree with a studying Design of Experiments used for wire bonding technique in several applications.

- Viktor works in several working groups in the automotive industry for qualifying components for the use in such hazard environments.

### **Course Outline**

MODULE 1: INTRODUCTIONS

- Intro to Design for Reliability

- DfR & Physics of Failure

#### MODULE 2: COMPONENTS

- Selection

- Critical Components

- Moisture Sensitivity Level

- Temperature Sensitivity Level

- Electrostatic Discharge

- Plating Material

- Miscellaneous

- Lifetime

- Derating & Uprating

MODULE 3: MECHANISMS & PHYSICS OF FAILURE

#### MODULE 4: PRINTED CIRCUIT BOARDS

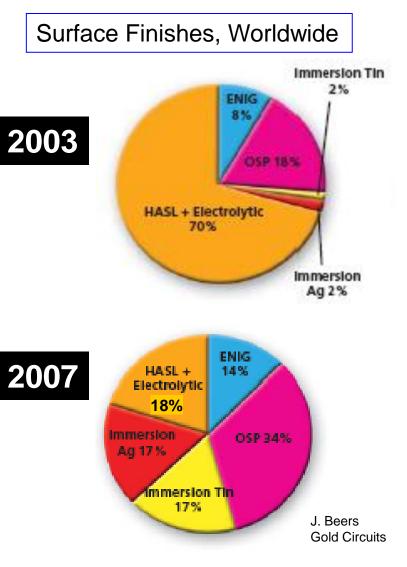

- Surface Finishes

- Cracking & Delamination

- Laminate Selection

- PTH Barrel Cracking

- CAF

- Strain/Flexure Issues & Pad Cratering

- Cleanliness

- Electrochemical Migration

MODULE 5: Printed Circuit Board Sourcing

MODULE 6: Focus on DfR in Manufacturing

### Design for Reliability (DfR) Defined

- <u>DfR</u>: A process for ensuring the reliability of a product or system during the design stage before physical prototype

- <u>Reliability</u>: The measure of a product's ability to

- ...perform the specified function

- ...at the customer (with their use environment)

- ...over the desired lifetime

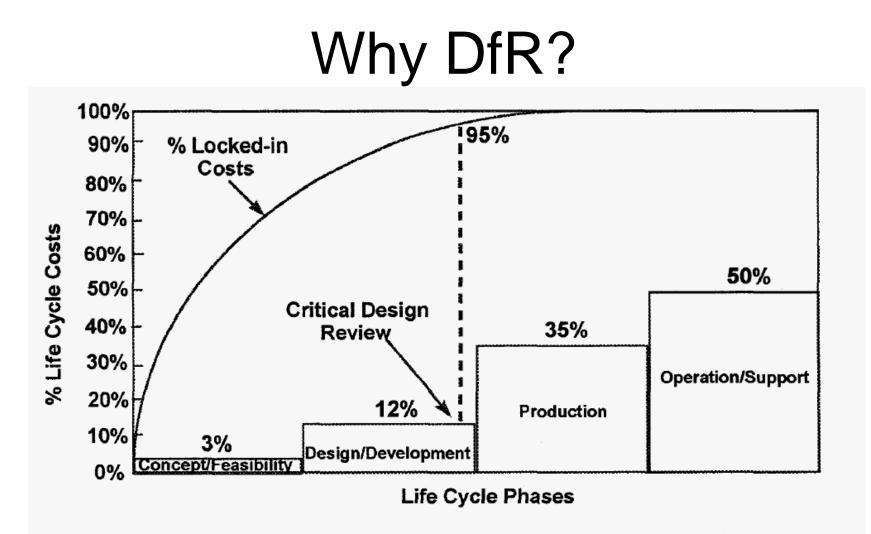

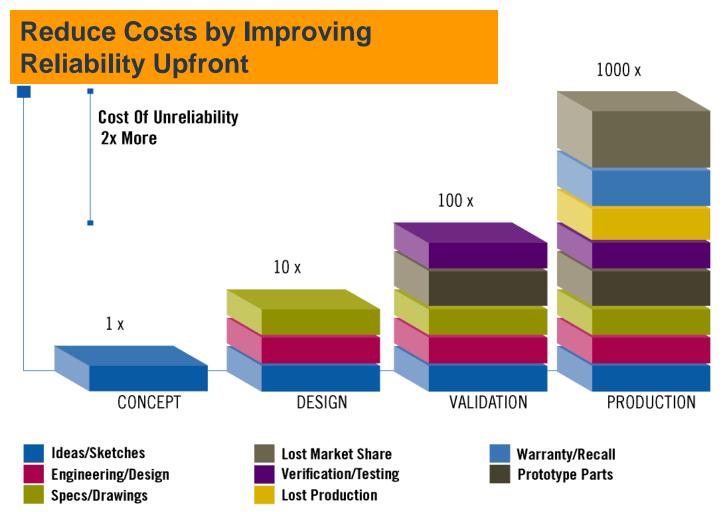

### Why Design for Reliability (DfR)?

- The <u>foundation</u> of a reliable product is a robust design

- -Provides margin

- Mitigates risk from defects

- Satisfies the customer

Architectural Design for Reliability, R. Cranwell and R. Hunter, Sandia Labs, 1997

## Why DfR? (continued)

### Who Controls Hardware Design?

**Electrical Designer**

- Component selection

- Bill of materials (BOM)

- Approved vendor list (AVL)

Mechanical Designer

- PCB Layout

- Other aspects of electronic packaging

Both parties play a critical role in minimizing hardware mistakes during new product development.

### When Do Mistakes Occur?

- Insufficient exchange of information between electrical design and mechanical design

- Poor understanding of supplier limitations

- Customer expectations (reliability, lifetime, use environment) are not incorporated into the new product development (NPD) process

"You don't know what you don't know" smthybridpackaging

### Reality of Design for Reliability (DfR)

- Ensuring reliability of electronic designs is becoming increasingly difficult

- Increasing complexity of electronic circuits

- Increasing power requirements

- Introduction of new component and material technologies

- Introduction of less robust components

- Results in multiple potential drivers for failure

# Reality (continued)

- Predicting reliability is becoming problematic

- Standard MTBF calculations can tend to be inaccurate

- A physics-of-failure (PoF) approach can be timeintensive and not always definitive (limited insight into performance during operating life)

### Limitations of Current DfR

- Too broad in focus (not electronics focused)

- Too much emphasis on techniques (e.g., FMEA and FTA) and not answers

- FMEA/FTA rarely identify DfR issues because of limited focus on the failure mechanism

- Overreliance on MTBF calculations and standardized product testing

- Incorporation of HALT and failure analysis (HALT is test, not DfR; failure analysis is too late)

- Frustration with 'test-in reliability', even HALT, has been part of the recent focus on DfR

### DfR and Physics of Failure (PoF)

- Due to some of the limitations of classic DfR, there has been an increasing interest in PoF (also known as: Reliability Physics)

- <u>PoF Definition</u>: The use of science (physics, chemistry, etc.) to capture an understanding of failure mechanisms and evaluate useful life under actual operating conditions

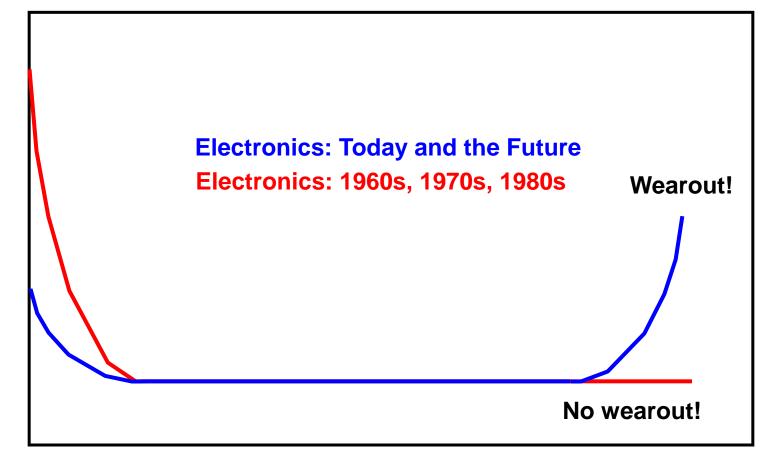

### Why PoF is Now Important

Failure Rate

Time

### PoF and Wearout

- What is susceptible to wearout in electronic designs?

- Ceramic Capacitors (oxygen vacancy migration)

- Memory Devices (limited write cycles, read times)

- Electrolytic Capacitors (electrolyte evaporation, dielectric dissolution)

- Resistors (if improperly derated)

- Silver-Based Platings (if exposed to corrosive environments)

- Relays and other Electromechanical Components

- Light Emitting Diodes (LEDs) and Laser Diodes

- Connectors (if improperly specified and designed)

- Tin Whiskers

- Integrated Circuits (EM, TDDB, HCI, NBTI)

- Interconnects (Creep, Fatigue)

- Plated through holes

- Solder joints

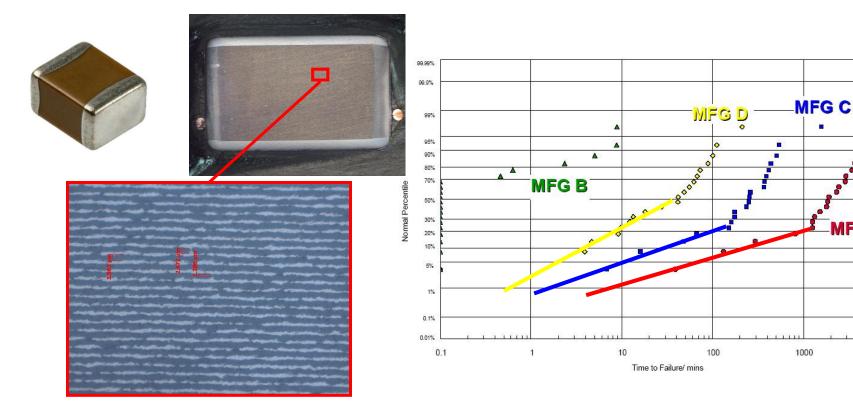

### Wearout (Ceramic Capacitors)

- Ceramic chip capacitors with high capacitance / volume (C/V) ratios

- Can fail in <u>less than one year</u> when operated at rated voltage and temperature

#### smthybridpackaging

MFG A

10000

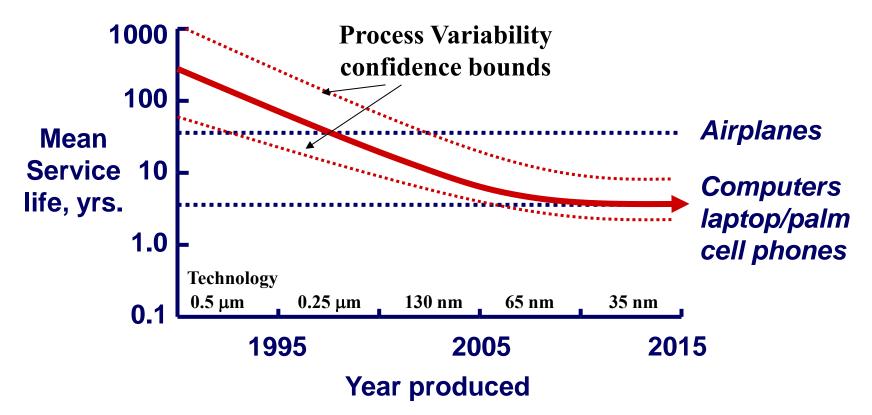

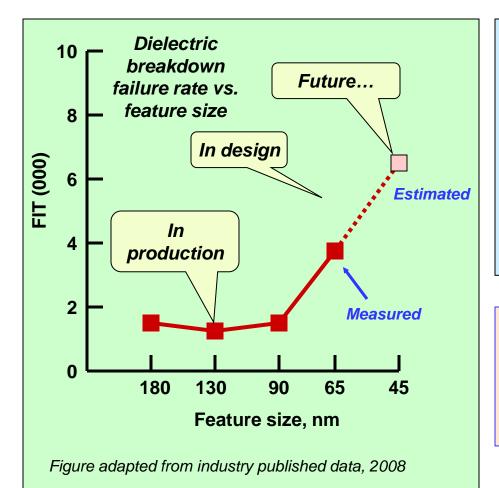

### Wearout (Integrated Circuits)

Known trends for TDDB, EM and HCI degradation

(ref: extrapolated from ITRS roadmap)

### IC Wearout (continued)

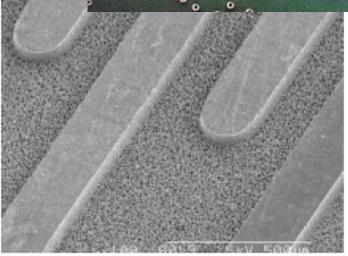

It is becoming more challenging to achieve very high reliability for products made with advanced technologies (90nm and smaller) *Phil Nigh, IBM Microelectronics*

"failure rate increases as we scale to smaller technologies...hard failures will present a significant and increasing challenge in future technology generations." *Pradip Bose, Jude A. Rivers, et al., IBM T.J.*

Watson Research Center

Increasing need to predict failure behavior before incorporating new technology in long-life systems

# IC Testing Falls Short

- Limited degree of mechanism-appropriate testing

- Only at transition to new technology nodes

- Mechanism-specific coupons (not real devices)

- Test data is hidden from end-users

- Questionable JEDEC tests are promoted to OEMs

- Limited duration (1000 hrs) hides wearout behavior

- Use of simple activation energy, with incorrect assumption that all mechanisms are thermally activated, can result in overestimation of FIT by 100X or more

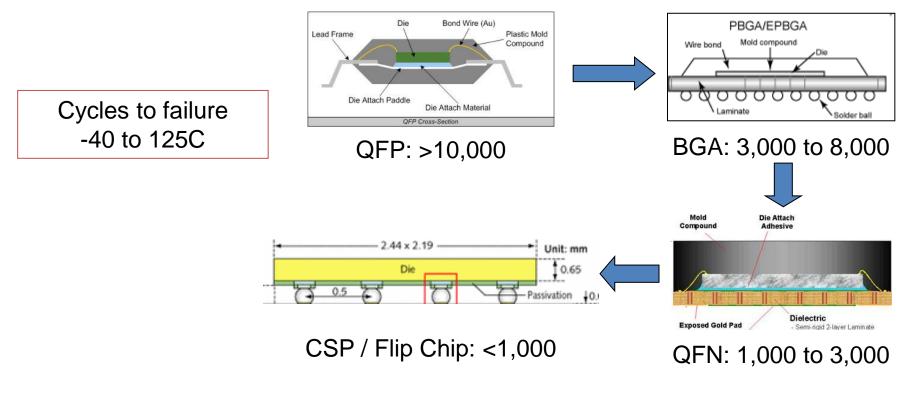

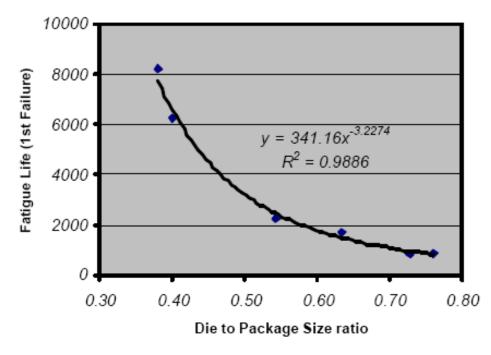

## Solder Joint (SJ) Wearout

- Elimination of leaded devices

- Provides lower RC and higher package densities

- Reduces compliance

### SJ Wearout (cont.)

- Design change: More silicon, less plastic

- Increases mismatch in coefficient of thermal expansion (CTE)

BOARD LEVEL ASSEMBLY AND RELIABILITY CONSIDERATIONS FOR QFN TYPE PACKAGES, Ahmer Syed and WonJoon Kang, Amkor Technology.

## Industry Testing of SJ Wearout

- JEDEC

- Specification body for component manufacturers

- JEDEC JESD4747H, February 2011

- Guidelines for new component qualification

- Requires <u>2300</u> cycles of 0 to 100C

- Testing is often done on <u>thin</u> boards

- IPC

- Specification body for electronic OEMs

- IPC 9701A, February 2006

- Recommends 6000 cycles of 0 to 100C

- Test boards should be <u>similar thickness</u> as actual design

## Industry and PoF

- VITA 51.2: Physics of Failure Reliability Predictions 2011

- Established by the standard bodies responsible for VME technology (open system architecture of real-time, modular embedded computing)

- VITA 51.2 provides rules and recommendations for the application of Physics of Failure (PoF) methods to reliability prediction of electronics at the board, packaging and component levels. It is a compilation in good faith, of existing physics of failure models selected by consensus of the working group of best practices in industry.

- IEC-TS-62239 2<sup>nd</sup> edition 2008: Process Management for Avionics

- FAA and Boeing expected to require PoF for IC wearout

# Implementing DfR / PoF

- Many organizations have developed DfR Teams to speed implementation

- Success is dependent upon team composition and gating functions

- <u>Challenges</u>: Classic design teams consist of electrical and mechanical engineers trained in the 'science of success'

- PoF requires the right elements of personnel and tools

### DfR / PoF Team

- Component engineer

- Mechanical / Materials engineer

- Electrical engineer

- Thermal engineer

- Depending upon power requirements

- Reliability engineer?

- Depends. Many classic reliability engineers provide <u>NO</u> value in the DfR / PoF process due to over-emphasis on statistical techniques and environmental testing

### **Component Selection**

- The process of creating the bill of materials (BOM) during the 'virtual' design process

- Before physical layout

- For some companies, this is during the creation of the approved vendor list (AVL)

Design-independent

### **Component Selection (continued)**

- As technology progresses, functional performance has become a limited aspect of the part selection process

- Other concerns are increasingly taking center stage

- Moisture sensitivity level (MSL)

- Temperature sensitivity level

- Electrostatic discharge (ESD) classification

- Manufacturability (Design for Assembly)

- Plating material

- Lifetime / Long-term reliability

- Sometimes Physics of Failure is required

### **Critical Components**

- Most small to mid-size organizations do not have the resources to perform a thorough part selection assessment on every part

- Does not excuse performing this activity

- Requires focusing on components critical to the design

- Critical Components: A narrowed list of components of most concern to the OEM

- Sensitivity of the circuit to component performance

- Number of components within the circuit

- Output from FMEA / FTA

- Past experiences

- Complexity of the component

- Industry-wide experiences

### Critical Components (Industry Experience)

- Optoelectronics

- High volume controls not always in place

- Wearout can initiate far before 20 years

- Low volume or custom parts

- Part is no longer a commodity item

- Memory devices

- Non-volatile memory has limited data retention time and write cycles

- Parts with mechanical movements (switches, relays, potentiostats, fans)

- Depending on environment, wear out can initiate far before 20 years

- Surface mount ceramic capacitors

- Assembly issues

# Critical Components (continued)

- New technologies or state-of-the-art

- At the limit of the manufacturer's capabilities

- MEMS, 45-nm technology, green materials, etc.

- Electronic modules

- Part is a miniature assembly (no longer a commodity item)

- Power components

- Fuses

- Susceptible to quality issues

- Electrolytic capacitors

- Depending on environment, wear out can initiate far before

20 years

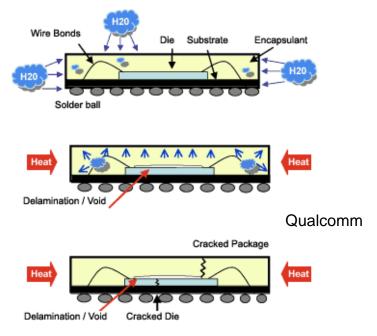

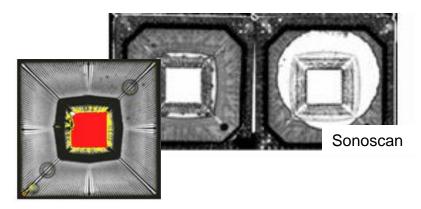

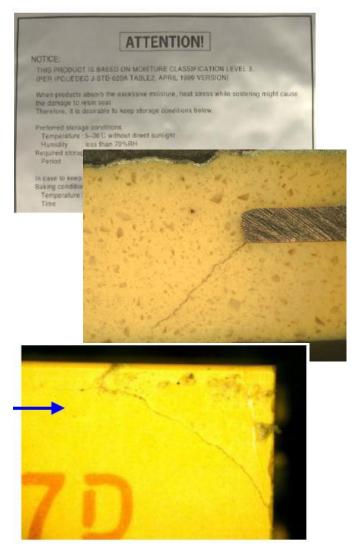

### Popcorning

- Moisture can be absorbed by polymeric material during transportation, storage and handling

- Epoxy encapsulant

- Die attach

- Printed substrate

- Trapped moisture can experience sudden liquid-gas phase transition during reflow

- Sudden volume increase due to vaporization

- Cracking and delamination sometimes accompanied by popping sound

- Driven by package design, materials, storage conditions and reflow parameters

### MSL Issues and Actions (continued)

- Most 'standard' components have a maximum MSL 3

- Components with MSL 4 and higher

- Large ball grid array (BGA) packages

- Encapsulated magnetic components (chokes, transformers, etc.)

- Optical components (transmitters, transceivers, sensors, etc.)

- Modules (DC-DC converters, GPS, etc.)

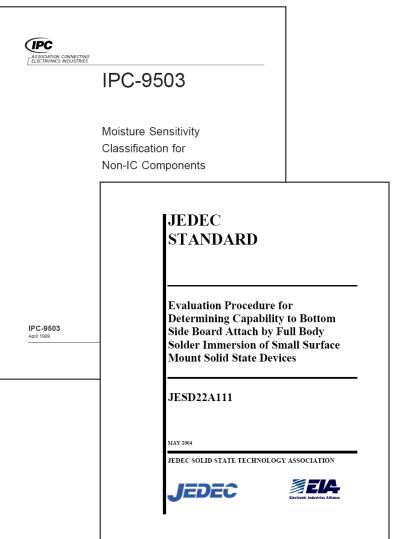

- MSL classification scheme in J-STD-020D is only relevant to SMT packages with integrated circuits

- Does not cover passives (IPC-9503) or wave soldering (JESD22A111)

- If not defined by component manufacturer, requires additional characterization

# Moisture Sensitivity Level (MSL)

- Popcorning controlled through moisture sensitivity levels (MSL)

- Defined by IPC/JEDEC documents J-STD-020D and J-STD-033B

- Higher profile in the industry due to transition to Pb-free and more aggressive packaging

- Higher die/package ratios

- Multiple die (i.e., stacked die)

- Larger components

| LEVEL | FLOOR LIFE             |               |

|-------|------------------------|---------------|

|       | TIME                   | CONDITIONS    |

| 1     | Unlimited              | ≤30 °C/85% RH |

| 2     | 1 year                 | ≤30 °C/60% RH |

| 2a    | 4 weeks                | ≤30 °C/60% RH |

| 3     | 168 hours              | ≤30 °C/60% RH |

| 4     | 72 hours               | ≤30 °C/60% RH |

| 5     | 48 hours               | ≤30 °C/60% RH |

| 5a    | 24 hours               | ≤30 °C/60% RH |

| 6     | Time on Label<br>(TOL) | ≤30 °C/60% RH |

### **MSL: Typical Issues and Action Items**

- Identify your maximum MSL

- Driven by contract manufacturer (CM) capability and OEM risk aversion

- Majority limit between MSL3 and MSL4 (survey of the MSD Council of SMTA, 2004)

#### Highest Level Assembled :

| Don't know | 26% |

|------------|-----|

| None used  | 4%  |

| MSL 2A     | 4%  |

| MSL 3      | 18% |

| MSL 4      | 18% |

| MSL 5      | 12% |

| MSL 5A     | 7%  |

| MSL 6      | 10% |

|            |     |

Cogiscan

- High volume, low mix: tends towards MSL4 Low volume, high mix: tends towards MSL3

- Not all datasheets list MSL

Can be buried in reference or quality documents

- Ensure that listed MSL conforms to latest version of J-STD-020

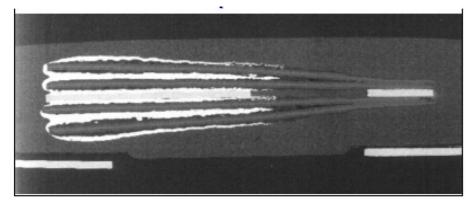

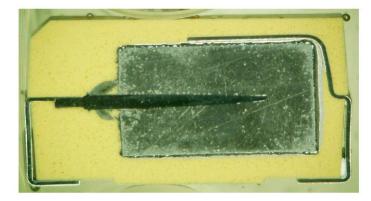

### Aluminum and Tantalum Polymer Capacitors

Aluminum Polymer Capacitor ↑

Tantalum Polymer Capacitor 7

### Popcorning in Tantalum/Polymer Capacitors

- Pb-free reflow is hotter

- Increased susceptibility to popcorning

- Tantalum/polymer capacitors are the primary risk

- Approach to labeling can be inconsistent

- Aluminum Polymer are rated MSL 3 (SnPb)

- Tantalum Polymer are stored in moisture proof bags (no MSL rating)

- Approach to Tantalum is inconsistent (some packaged with dessicant; some not)

- Material issues

- Aluminum Polymer are rated MSL 3 for eutectic (could be higher for Pb-free)

- Sensitive conductive-polymer technology may prevent extensive changes

- Solutions

- Confirm Pb-free MSL on incoming plastic encapsulated capacitors (PECs)

- More rigorous inspection of PECs during initial build

### **Temperature Sensitivity**

- Limits on process temperatures provided by component manufacturer

- Components of concern with SnPb (220C peak) included RF devices and some optoelectronic components

- Broader issue due to introduction of Pb-free processes (260C peak)

- Initially limited: SnPb reflow sensitive components, SMT connectors, ceramic capacitors, SMT electrolytic capacitors

- Primary issue for some OEMs

- Current component packaging technology is insufficiently robust

- Numerous components in a telecom / enterprise design now have peak temperatures below 260C

# Component Selection for ESD

- Industry movement to decreasing feature sizes and high frequency technology

- $-90 \text{nm} \rightarrow 65 \text{nm} \rightarrow 45 \text{nm}$

- GaAs / SiGe desirable at high GHz

- Increasing ESD risks

- More parts are ESD susceptible

- ESD sensitivity is increasing (is Class 0 still sufficient?)

### Design for ESD Prevention: What Do You Need to Do?

- ESD Protection is necessary at the IC, component package and system level

- Different approaches are needed to achieve reliable protection

- Designing for ESD impacts both the product design and the manufacturing process controls

- What technologies are available to assure a reliable ESD protected product?

- At the IC level

- At the component package level

- At the system level

### Good General Design Practices for ESD Prevention

- Know the ESD rating for each part, and select parts (where possible) for the best ESD rating

- Identify all ESD Sensitive Parts on drawings

- Mark Locations of ESD Sensitive parts on the Board with the ESD symbol

- Consider the entire System (Design) as ESD Sensitive

- Use ESD Protection on all susceptible parts (not just System I/Os)

- Box or System I/O

- ESD Rating < Class 2 IEC 1000-4-2 (4000V) MANDATORY

- Internal Components (not exposed to outside connectors)

- ANSI/ESDA/JEDEC JS-001-2011, Human Body Model (HBM) Component Level

- ESD Rating <= Class 1 MANDATORY</li>

- ESD Rating < Class 2 WHEREVER POSSIBLE</li>

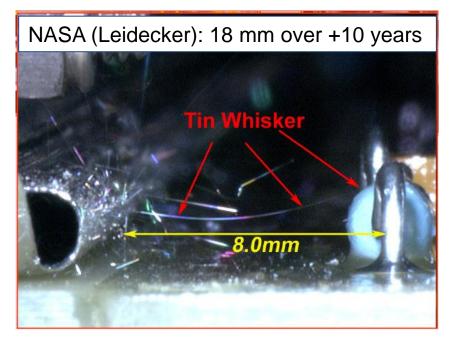

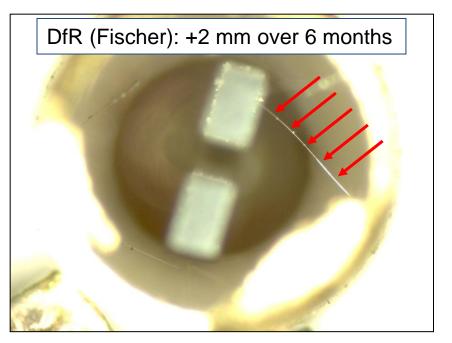

## DfR and Tin Whiskers

- The first step is to focus DfR on <u>critical</u> <u>components</u>

- Critical components are based upon three pieces of knowledge

- The overwhelming majority of tin-plated electronic parts are matte tin over copper

- Matte tin over copper produces whiskers of a finite length

- Whiskers tend to only break off during handling

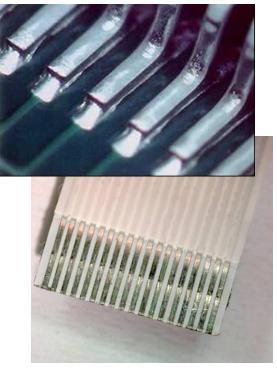

### Where are the Scary Whiskers?

- When do really long whiskers occur?

- Usually bright tin and/or plating over a substrate material other than copper (brass, bronze, steel, etc.)

Tin (bright?) over steel

Tin (matte?) over brass

### **Critical Components**

- Spacings of less than 500 microns

- Parts with 0.8 mm lead pitch or less

- 0201 chip components

- Metal can housing

- Contact points (connector flex circuitry)

- Stress gradients could change maximum length

- Welds (electrolytic capacitors)

- Stress gradients could change maximum length

- Note: Some organizations specify the critical spacing as 350 microns

- 0.65 mm pitch or less

# How to Mitigate?

- There are three basic approaches to mitigation

- Data Gathering and Monitoring

- Part Manufacturer Mitigation

- Steps offered by your suppliers

- Equipment Manufacturer (OEM) Mitigation

Steps you have to perform yourself

### Data Gathering and Monitoring

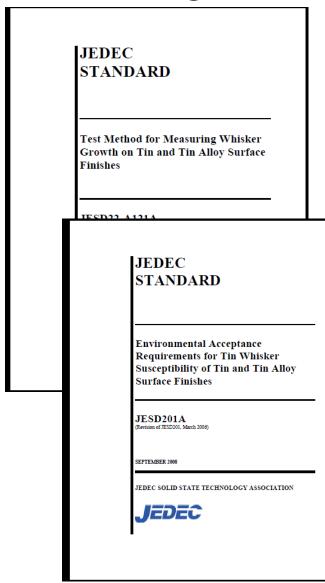

- Driven by iNEMI and JEDEC (JESD22A121A, JESD201A, JP002)

- Industry recommended qualification tests

- Ambient (30C/60%RH, 4000 hrs)

- Elevated (55C/85%RH, 4000 hrs)

- Cyclic (-40 to 85C, 1500 cycles)

- Shorter test times for consumer products

- Use manufacturer's data, require thirdparty testing, or perform your own

- Visual inspection should be performed properly

- <u>http://nepp.nasa.gov/whisker/backgrou</u> <u>nd/index.htm#q6</u>

- Few to no military/avionics manufacturers are using this approach

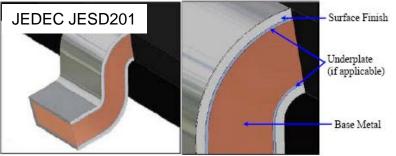

### Part Manufacturer Mitigation

- Nickel underplate between the tin plating and the copper leadframe

- Some question about effectiveness (IBM vs. TI)

- Some question about minimum thickness

- iNEMI (article) recommends 2 microns

- ATIS requires 2 microns

- PC manufacturer requires 1.2 microns

- JP-002 March 2006 requires 0.5 microns

- Might not help for ceramic substrate due to CTE mismatch

- Anneal for 1 hour at 150°C within 24 hours of plating

- This is the approach for Freescale

- Fusing (melting of tin through dipping in a hot oil bath)

- Excellent field history; must be performed soon after plating

- Minimum plating thickness

- Some question about minimum thickness

- Telecom manufacturer requires 10 microns

- JP-002 March 2006 recommends 7 microns minimum, 10 microns nominal

### Part Manufacturer Mitigation (continued)

- Some component manufacturers claim proprietary whisker-free plating formulation

- Be skeptical; require Statistical Process Control

- Tin bismuth alloy finishes

- Mitigation not definitive

- Low melting point of SnPbBi ternary might pose problems in mixed assemblies

- Some experimental evidence suggests SnPb-plating and SnBi solder is a greater risk

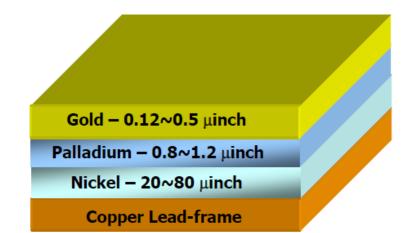

- Request palladium (Pd) plating NiPdAu

- Increasingly offered as an option, even to low volume customers (medical, industrial controls, etc.)

- Most manufacturers have moved to Pd as a standard plating for fine-pitch components

### Leadframe Platings

Palladium and SnBi are seeing an increasing market share due to concerns with tin whiskering

Ni-Pd-Au Finish, Cypress Semiconductor

| Company                | Package          | Plating                               |  |  |

|------------------------|------------------|---------------------------------------|--|--|

| Intel                  | QFP / TSOP       | Sn <sup>ill</sup>                     |  |  |

| Samsung                | QFP / TSOP       | NiPdAu                                |  |  |

| Texas Instruments      | QFP / TSOP       | NiPdAu                                |  |  |

|                        | TSOP (Discretes) | NiPdAu                                |  |  |

| Toshiba                | TSOP (Memory)    | SnAg or SnCu                          |  |  |

|                        | TSOP (LSI)       | NiPdAu or SnAg or SnBi                |  |  |

| STMicroelectronics     | QFP / TSOP       | NiPdAu                                |  |  |

| 1                      | QFP              | Sn or SnPb                            |  |  |

| Infineon               | TSOP             | NiPdAu                                |  |  |

| Demoses Teshnolom      | QFP              | Mostly Sn-Cu, Sn-Bi; some NiPdAu      |  |  |

| Renesas Technology     | TSOP             | Mostly NiPdAu, with some Sn-Cu, Sn-Bi |  |  |

| Sony                   | QFP / TSOP       | Pd or SnPb                            |  |  |

| Dhiling /NYD           | QFP              | Sn                                    |  |  |

| Philips/NXP            | TSOP             | NiPdAu                                |  |  |

| Hynix                  | TSOP             | SnBi                                  |  |  |

| Freescale              | QFP / TSOP       | Sn                                    |  |  |

| NEC                    | QFP / TSOP       | Sn, SnBi, or NiPdAu                   |  |  |

| Micron                 | TSOP             | Sn, SnPb                              |  |  |

| Mataurahita (Danaaania | QFP              | Pd                                    |  |  |

| Matsushita/Panasonic   | TSOP             | SnBi                                  |  |  |

| AMD                    | QFP              | Sn, SnCu, or SnPb                     |  |  |

| IBM                    | QFP              | N/A                                   |  |  |

| Qualcomm               | N/A              | N/A                                   |  |  |

| E-iii-i                | QFP              | SnBi                                  |  |  |

| Fujitsu                | TSOP             | SnBi                                  |  |  |

|                        | QFP              | SnBi, NiPdAu                          |  |  |

| Sharp                  |                  |                                       |  |  |

# **OEM** Mitigation

- Four Options

- Procurement, Re-packaging, Post-plate or dip, Conformal coat

- Procurement / Design

- Select only components with SnPb or Pd plating

- May require complete change in circuit design if alternative component required

- Rarely performed (functionality trumps reliability)

- Subcontract packaging or Re-packaging

- SnPb or Pd plated leadframes

- Rarely performed (cost, risk of damage)

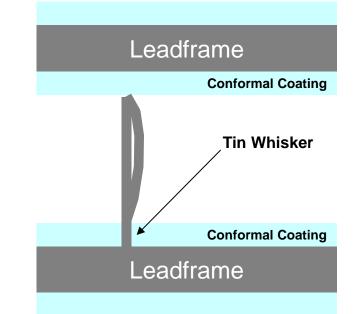

### Tin Whiskering – Conformal Coating

- Potential to provide a dual barrier

- Prevention or delay of whiskering

- Some indication of a delay in whiskering (Rollins / Minter)

- Short tin whiskers will eventually penetrate all current conformal coatings

- No definitive trend in regards to coating properties

- Buckling

- Based on calculations (Leidecker, NASA)

- Not experimentally proven

- Limitations

- Insufficient coverage at leads (gravity)

- Problems with conformal coat may outweigh possible risk avoidance

- Current status:

- Development of whisker-resistant coating

- Assessment of single vs. double coating

- <u>http://nepp.nasa.gov/WHISKER/experiment/index.html</u>

### Component Selection (Misc)

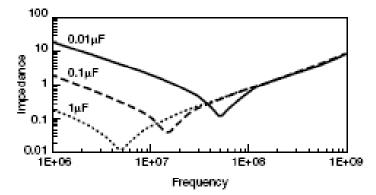

### Ceramic Capacitors (Cyclic Voltage)

http://www.avxcorp.com/docs/techinfo/parasitc.pdf

- Reports of field failures of MLCC in AC or pulsed DC voltage

- Piezoelectric effect

- Variant voltage will vary internal stresses, potentially inducing fatigue behavior

- With high frequency ripple current, capacitor can vibrate (resonate).

- Fatigued specimens can contain scattered microcracks

- Decrease in capacitance; increase in leakage current

- Concern at hundreds of kHz

- Decreases with increasing capacitance, X7R -> Y5V

- Avoid or use AC-rated capacitors

Figure 5. 1206, X7R impedance curves for a variety of capacitance values.

| Case Size |        | Resonance Frequency |  |

|-----------|--------|---------------------|--|

| English   | Metric | Resonance Frequency |  |

| 3025      | 7563   | 250 - 750 kHz       |  |

| 2220      | 5750   | 300 - 900 kHz       |  |

| 1812      | 4532   | 400 - 1200 kHz      |  |

| 1210      | 3225   | 600 - 1200 kHz      |  |

| 1206      | 3216   | 600 - 1600 kHz      |  |

| 0805      | 2012   | 900 - 1800 kHz      |  |

| 0603      | 1608   | N/A                 |  |

| 0402      | 1005   | N/A                 |  |

Nippon Chemi-con, CAT.No.E1002I

Sang-Joo Kim and Qing Jiangy, Microcracking and electric fatigue of polycrystalline ferroelectric ceramics, Smart Mater. Struct. 5 (1996)

# **Resistors (High Resistance)**

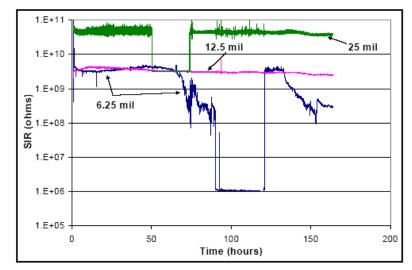

- Board surfaces can be susceptible to periodic SIR drops

- Especially with no-clean

- Duration as short as 1 min

- Down to 1 MegaOhm

- Fine pitch, high voltage especially susceptible

- Can interfere with high resistance resistors

- Especially chip resistors

- Intermittent in nature

- Avoid values > 500 kOhms if used for sensing or calibration

- Consider lower values in series

- Use guard banding or cutouts

No-clean solder paste, 40/93 at 24 VDC

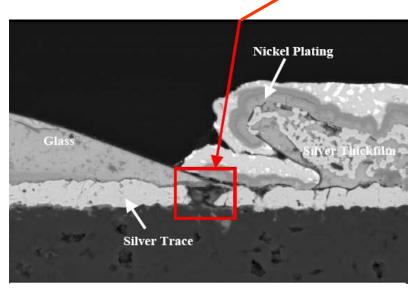

### Sulfide Corrosion of Thick Film Resistors

- Sulfur dioxide (SO<sub>2</sub>) and hydrogen sulfide (H<sub>2</sub>SO<sub>4</sub>) in environment

- Sources: Black rubber, industrial pollution

- Attacks silver material under passivation/ termination

- Creates nonconductive silver sulfide

- Drivers

- Cracking/separation of coating/termination

- Poor manufacturing

- Thermal shock

- Potting or conformal coating

- Seems to act as a 'sponge'

- Holds SO<sub>2</sub> molecules in place

- Electrical opens within 1-4 years

- Avoidance

- Orient parallel to solder wave

- Entrance side can experience thermal shock

- Avoid hand soldering/rework

- Sulfur-resistant PdAg material (KOA)

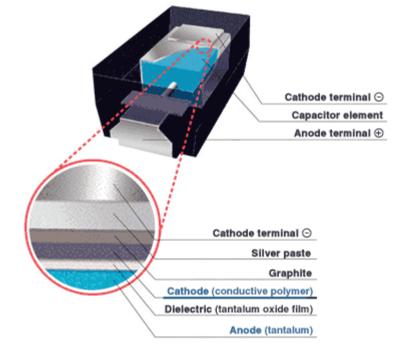

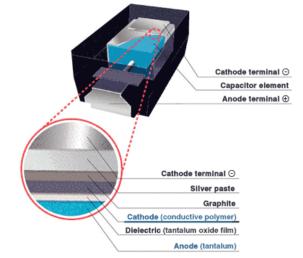

### **Tantalum and Polymeric Capacitors**

- Tantalum capacitors are selected for volumetric efficiency

- Older technology can be susceptible to ignition

- Requires aggressive derating (50% or greater)

- Sensitive to higher temperatures (>85C) and certain circuits

- Newer, polymeric capacitors are available

- Significant reduction in ESR

- Less derating

- No risk of ignition

|                                     | MnO <sub>2</sub><br>(27Batches) | Ta-Poly KO<br>(37 Batches) | Alum-Poly – AO<br>(78 Batches) |

|-------------------------------------|---------------------------------|----------------------------|--------------------------------|

| 100 PPM FR<br>% V <sub>Rated</sub>  | 68%                             | 114%                       | 235%                           |

| @50% V <sub>Rated</sub><br>FR(PPM)  | 9                               | 0                          | 0                              |

| @80% V <sub>Rated</sub><br>FR(PPM)  | 458                             | 5                          | 0                              |

| @90% V <sub>Rated</sub><br>FR(PPM)  | 1,700                           | 19                         | 0                              |

| @100% V <sub>Rated</sub><br>FR(PPM) | 2,943                           | 255                        |                                |

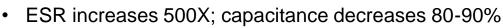

# **Electrolytic Capacitors**

- Voltage

- Maintain a minimum of 25-33% of rated voltage (maintains the dielectric)

- Temperature

- Maintain adequate distance from 'hot' components

- Power resistors, IGBTs, etc.

- Seems to accelerate time to failure and can induce explosive rupturing

- 105C rated capacitors can be an issue at lower temperatures (below -40C)

- Ripple Current

- Up to 100% or greater of rated ripple current

- Need to calculate/measure case temperature rise

- Equivalency on bill of materials is often not maintained

- Equivalent Series Resistance (ESR)

- Often not specified on the component data sheet

## Separable Connectors

- Separable Connectors

- One of the most common failure sites

- First thing maintenance checks (plug / unplug)

- Hardware Design Rules

- Blind insertion increases risk of damage or mismating (consider flex or rigid-flex)

- All connectors should be keyed

- Prevents reversal of I/O pins

- Use positively retained connectors

- Avoid use of sockets

- Specify material and thickness

### Separable Connectors [Gold (Au)]

#### Connections and environments

- Hi-speed digital or critical connections

- Low voltage (< 5V), low current (< 10mA)</p>

- Corrosive environment (gases such as H<sub>2</sub>S, SO<sub>2</sub>, Cl<sub>2</sub>)

- Risk of micromotion (< 2.5 μm)</li>

- Material specifications

- Be-Cu or P-bronze base pins

- Nickel underplate (250 min)

- Soft gold (Au) plating

- 10 min (single insertion); 30 min (50 insertions); 70 min (hirel)

- Porosity spec

- No gold flash

- Contact specifications

- 50-100 grams contact force

- Minimum of 2 contacts; 4 preferred

- Adequate contact wipe 0.010" min.

- No mating with tin plating

# Separable Connectors [Tin (Sn)]

- Connections and environment

- Power connections

- Benign

- Tin plating design specification

- 100 grams-force, 100 microinches (Tin Commandments)

# DfR (Miscellaneous)

• Components taller then 1 inch

- Use of staking compound to adhere to board

### Component Selection (Lifetime)

# **Component Lifetime**

- What parts are susceptible to long-term degradation in electronic designs?

- Ceramic Capacitors (oxygen vacancy migration)

- Memory Devices (limited write cycles, read times)

- Electrolytic Capacitors (electrolyte evaporation, dielectric dissolution)

- Resistors (if improperly derated)

- Silver-Based Platings (if exposed to corrosive environments)\*

- Relays and other Electromechanical Components

- Light Emitting Diodes (LEDs) and Laser Diodes

- Connectors (if improperly specified and designed)\*

- Tin Whiskers\*

- Integrated Circuits (EM, TDDB, HCI, NBTI)

- Interconnects (Creep, Fatigue)

- Plated through holes

- Solder joints

Industry-accepted models exist \*Already discussed

### Lifetime Example: Memory Devices

• Limited lifetime based on read-write cycles and retention time

| Parameter      | Minimum Guarantee | Units                |  |

|----------------|-------------------|----------------------|--|

| Endurance      | 100,000           | Data changes per bit |  |

| Store cycles   | 1,000,000         | Store cycles         |  |

| Data retention | 100               | Years                |  |

Some memory devices provide data retention time for different operating temperatures (20 years at 125°C and 10 years at 150°C).

# Light and Laser Diode Wearout

- Increasing importance with adoption of optical communications and LCD backlight

- Standard model for on-die wearout is:

$$t_f = A(J)^n \exp\left(\frac{E_a}{kT}\right)$$

- where A is a constant, J is the current density, n is an exponent

- n =1.5 2 for a large number of different LED structures

- n = 6 7 for laser diodes with facet passivation

- Expression applies for units run in automatic current control (ACC), or constant current.

- Units run at constant output power (APC), power substitutes current density (n may be higher)

- Some models will combine power and current density

- Note: Model does not apply to die attach fatigue

- A risk in high power, cyclic applications

# Light and Laser Diode Wearout

- Estimated lifetime is not always provided

- When lifetime is provided, it is MTBF at room temp.

- Time to 5% failure can be half the time

- Time to failure at 40C can be half the time

- 50K hrs can turn into 12.5K hrs

- Lifetime is not always be equivalent to failure

- 50% reduction in intensity

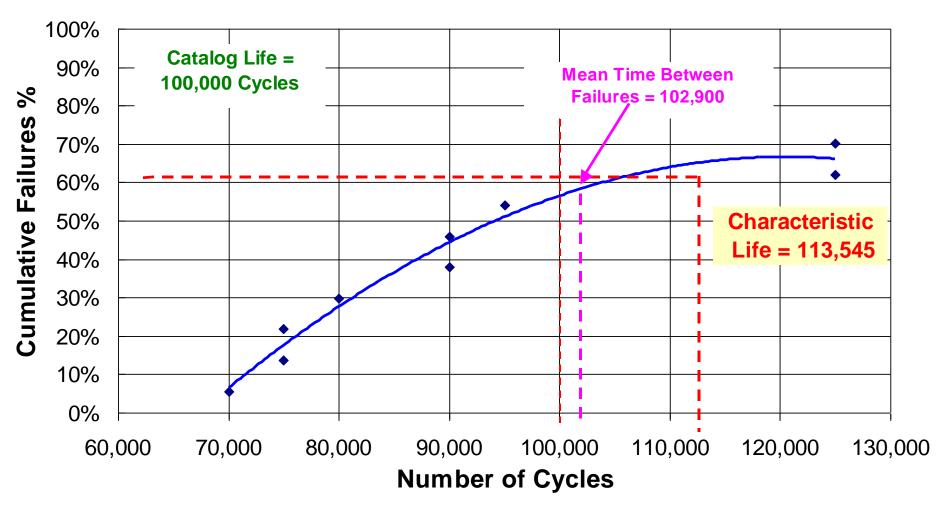

### Lifetime Example: Relays/Switches

- Relays are an electromechanical switch

- Minimum of four I/Os

- Control voltage

- Signal voltage

- What are the major concerns in regards to relay reliability?

- Number of cycles to failure

- Long-term non-use

- Power dissipation and contact resistance (heating and voltage drops)

# Relays/Switches (continued)

- Selection of appropriate plating

- Idle for long periods of time: Gold contacts

- Numerous cycles: AgCd contacts

- Sealed packages if cleaning operations

- Use of protective devices

- Diode, resistor, capacitor, varistor, etc.

- Prevents arcing during switching (accelerates degradation)

- Must be nearby

- Temperature rise

- Wide range of contact resistance in specifications

- Ensure margin between design life requirements and manufacturer's specifications

### Wearout of Relays/Switches

### **Derating and Uprating**

## **Component Ratings**

- Definition

- A specification provided by component manufacturers that guides the user as to the appropriate range of stresses over which the component is guaranteed to function

- Typical parameters

- Voltage

- Current

- Power

- Temperature

MSP430FG43x MIXED SIGNAL MICROCONTROLLER

SLAS380B - APRIL 2004 - REVISED JUNE 2007

#### absolute maximum ratings over operating free-air temperature (unless otherwise noted)<sup>†</sup>

| $ \begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                 |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not |  |

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. NOTE: All voltages referenced to V<sub>SS</sub>. The JTAG fuse-blow voltage, V<sub>FB</sub> is allowed to exceed the absolute maximum rating. The voltage is applied

to the TDI/TCLK pin when blowing the JTAG fuse.

#### recommended operating conditions

|                                                                                                                                                                       | MIN | NOM MAX | UNITS |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------|-------|

| Supply voltage during program execution (see Note 1), V <sub>CC</sub> (AV <sub>CC</sub> = DV <sub>CC1/2</sub> = V <sub>CC</sub> )                                     | 1.8 | 3.6     | V     |

| Supply voltage during program execution, SVS enabled, PORON=1<br>(see Note 1 and Note 2), V <sub>CC</sub> (AV <sub>CC</sub> = DV <sub>CC1/2</sub> = V <sub>CC</sub> ) | 2   | 3.6     | v     |

| Supply voltage during flash memory programming (see Note 1),<br>V <sub>CC</sub> (AV <sub>CC</sub> = DV <sub>CC1/2</sub> = V <sub>CC</sub> )                           | 2.7 | 3.6     | v     |

| Supply voltage, V <sub>SS</sub> (AV <sub>SS</sub> = DV <sub>SS1/2</sub> = V <sub>SS</sub> )                                                                           | 0   | 0       | V     |

| Operating free-air temperature range, T <sub>A</sub>                                                                                                                  | -40 | 85      | °C    |

#### IGBT MODULE (U series) 600V / 100A / PIM

Features

Low Vcɛ(sat)

Compact Package

P.C. Board Mount Module

Converter Diode Bridge Dynamic Brake Circuit

#### Maximum ratings and characteristics Absolute maximum ratings (Tc=25°C unless otherwise specifie

| tem                                                                                                                | e                               | Symbol    | Condition           | Rating      | Unit             |

|--------------------------------------------------------------------------------------------------------------------|---------------------------------|-----------|---------------------|-------------|------------------|

| Inverter                                                                                                           | Collector-Emitter voltage       | Vces      |                     | 600         | V                |

|                                                                                                                    | Gate-Emitter voltage            | VGES      |                     | ±20         | V                |

|                                                                                                                    | Collector current               | lc.       | Continuous          | 100         | A                |

|                                                                                                                    |                                 | ICP       | 1ms                 | 200         | A                |

| Ě                                                                                                                  |                                 | -lc       |                     | 100         | A                |

|                                                                                                                    |                                 | -Ic pulse | 1ms                 | 200         |                  |

|                                                                                                                    | Collector power disspation      | Pc        | 1 device            | 378         | W                |

| Brake                                                                                                              | Collector-Emitter voltage       | VCES      |                     | 600         | V                |

|                                                                                                                    | Gate-Emitter voltage            | VGES      |                     | ±20         | V                |

|                                                                                                                    | Collector current               | k         | Continuous          | 50          | A                |

|                                                                                                                    |                                 | ICP.      | 1ms                 | 100         | A                |

|                                                                                                                    | Collector power disspation      | Pc        | 1 device            | 187         | W                |

|                                                                                                                    | Repetitive peak reverse voltage | VRRM      |                     | 600         | V                |

| *                                                                                                                  | Repetitive peak reverse voltage | VRRM      |                     | 800         | V                |

| ert.                                                                                                               | Average output current          | b         | 50Hz/60Hz sine wave | 100         | A                |

| Converter                                                                                                          | Surge current (Non-Repetitive)  | IFSM      | Tj=150°C, 10ms      | 700         | A                |

|                                                                                                                    | Pt (Non-Repetitive)             | R         | half sine wave      | 2450        | A <sup>2</sup> s |

| Operating junction temperature                                                                                     |                                 | Tj        |                     | +150        | °C               |

| Storage temperature                                                                                                |                                 | Tstg      |                     | -40 to +125 | °C               |

| Isolation between terminal and copper base *2<br>voltage between thermistor and others *3<br>Mounting screw torque |                                 | Viso      | AC : 1 minute       | AC 2500     | V                |

|                                                                                                                    |                                 |           |                     | AC 2500     | V                |

|                                                                                                                    |                                 |           |                     | 3.5 *1      | Nm               |

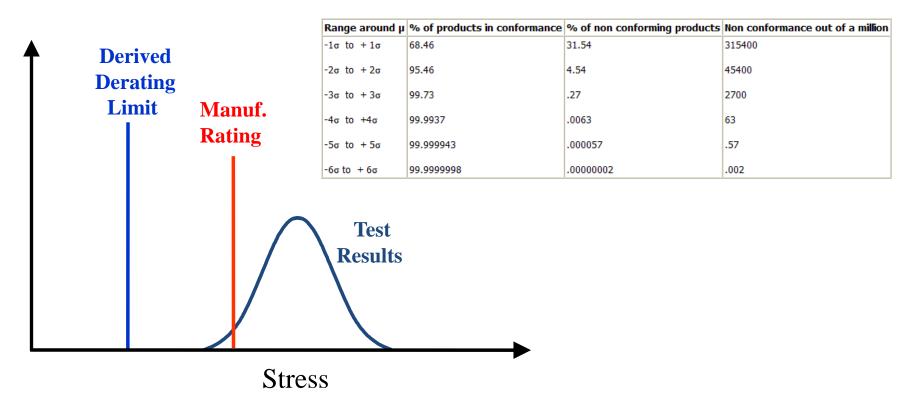

# Derating

- Derating is the practice of limiting stress on electronic parts to levels below the manufacturer's specified ratings

- Guidelines can vary based upon environment

- ("severe, protected, normal" or "space, aircraft, ground")

- One of the most common design for reliability (DfR) methods

- Goals of derating

- Maintain critical parameters during operation (i.e., functionality)

- Provide a margin of safety from deviant lots

- Achieve desired operating life (i.e., reliability)

- Sources of derating guidelines

- Governmental organizations and 3<sup>rd</sup> parties

- OEM's

- Component manufacturers

- Derating is assessed through component stress analysis

## **Derating Guidelines (Examples)**

| Part Type                   | Derating parameters            | Severe                  | Benign                  |  |

|-----------------------------|--------------------------------|-------------------------|-------------------------|--|

| Aluminium electrolytic caps | Voltage (% max rated)          | 70%                     | 80%                     |  |

|                             | Temperature (°C)               | T <sub>max</sub> - 20°C | T <sub>max</sub> - 20°C |  |

| Ceramic capacitors          | Voltage (% max rated)          | 60%                     | 70%                     |  |

|                             | Temperature (°C)               | T <sub>max</sub> − 10°C | T <sub>max</sub> - 10°C |  |

| Solid tantalum capacitors   | Voltage (% max rated)          | 70%                     | 80%                     |  |

|                             | Temperature (°C)               | T <sub>max</sub> - 20°C | T <sub>max</sub> - 20°C |  |

|                             | Reverse voltage (% max fwd)    | 2%                      | 2%                      |  |

| Signal diodes               | Forward current (% max rated)  | 90%                     | <100%                   |  |

|                             | Reverse voltage (% max rated)  | 70%                     | 80%                     |  |

|                             | Max. junction temperature      | 95°C                    | 115°C                   |  |

| Chip resistors              | Power dissipation(% max rated) | 50%                     | 70%                     |  |

| Digital MOS and bipolar ICs | Fanout (% max rated)           | 90%                     | <100%                   |  |

|                             | Frequency (% max rated)        | 90%                     | <100%                   |  |

|                             | Output current (% max rated)   | 90%                     | <100%                   |  |

|                             | Max. junction temperature      | 95°C                    | 115°C                   |  |

| Linear MOS and bipolar ICs  | Frequency (% max rated)        | 90%                     | <100%                   |  |

|                             | Output current (% max rated)   | 90%                     | <100%                   |  |

|                             | Max. junction temperature      | 95°C                    | 115°C                   |  |

### Criticality of Component Stress Analysis

- Failure to perform component stress analysis can result in higher warranty costs, potential recalls

- Eventual costs can be in the millions of dollars

- Perspective from Chief Technologist at major Original Design Manufacturer (ODM)

"...based on our experience, we believe a significant number of field returns, and the majority of no-trouble-founds (NTFs), are related to overstressed components."

# **Derating Failures**

- Where are the derating mistakes?

- Problem #1: Designers do not derate

Failure to perform component stress analysis

- Problem #2: Derating does not have a practical or scientific foundation

- Extraordinary measures are taken when inappropriate

- Derating is excessive: 'The more, the better' rule

## Failure to Derate

- Analog / Power Designs

- Derating is typically overlooked during transient events

- Especially turn-on, turn-off

- Digital

- Excessive number of components and connections tends to limit attempts to perform component stress analysis

# The Foundation of Derating

- To be effective, derating must have a practical and scientific foundation

- Problem: Manufacturer's ratings are not always based on a practical and scientific foundation

- Manufacturers' viewpoint

- Ratings are based on specific design rules based on materials, process, and reliability testing

- The reality

- Ratings can be driven by tradition and market forces as much as science

- Best practice

- Based on data from field returns

- Based on test to failure qualification (especially for new suppliers)

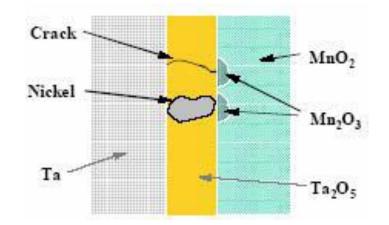

### Scientific Approach to Derating (Ta Caps)

#### **High Impedance Circuits**

Self healing in Ta capacitors involves leakage paths in the MnO<sub>2</sub> being healed by the transformation to the higher resistance compound Mn<sub>2</sub>O<sub>3</sub>

- Process requires enough current to allow internal temperatures to reach 500°C

- Small amounts of current (< 50 uA) will prevent self healing</li>

Leads to degradation and potential component failure

- Avoid use in circuits with impedances greater than 100 k $\Omega$

# **Derating Decision Tree**

- <u>Step 1</u>: Derating guidelines should be based on component performance, not ratings

- Test to failure approach (i.e., HALT of components)

- Quantifies life cycle cost tradeoffs

- For smaller OEMs, limit this practice to critical components

### Derating based on Test to Failure

- OEM was concerned with voltage rating of tantalum capacitors after 2 reflows and use on low resistance line

- Performed step stress surge test (SSST)

- Derived voltage derating based on a sub-ppm failure rate

## **Derating Decision Tree (continued)**

- <u>Step 2</u>: Derating guidelines should be based on recommendations from the component manufacturer

- They built it; they should know it

- Don't trust the manufacturer? Use someone else

- <u>Step 3</u>: Derating guidelines should be based on customer requirements

- <u>Step 4</u>: Derating guidelines should be based industry-accepted specification/standard

### Be flexible, not absolute

### Robustness - Components

- Concerns

- Potential for latent defects after exposure to Pbfree reflow temperatures

- $_{\circ}$  215°C 220°C peak → 240°C 260°C peak

- Drivers

- Initial observations of deformed or damaged components

- Failure of component manufacturers to update specifications

- Components of particular interest

- Aluminum electrolytic capacitors

- Ceramic chip capacitors

- Surface mount connectors

- Specialty components (RF, optoelectronic, etc.)

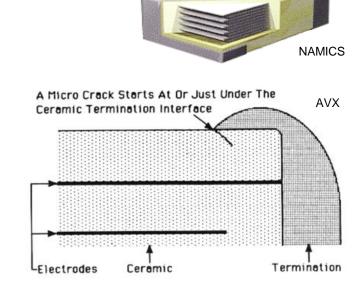

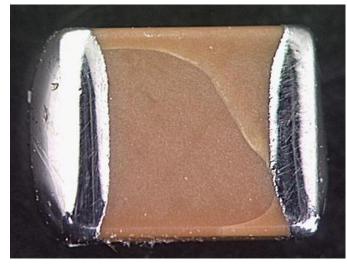

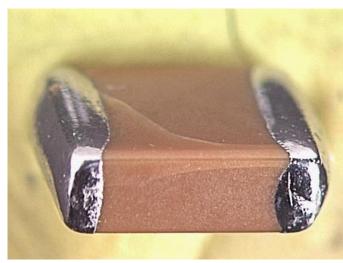

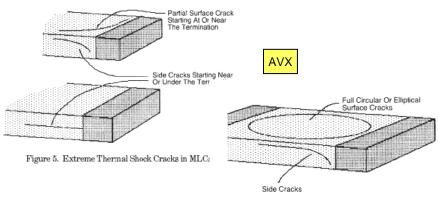

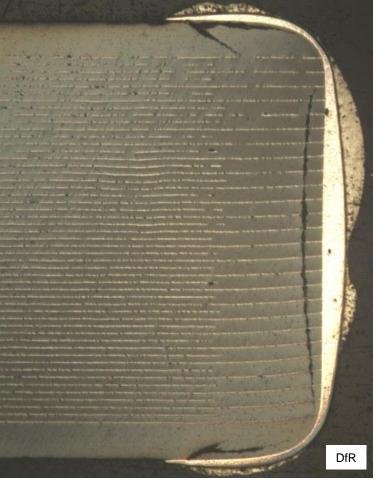

### Ceramic Capacitors (Thermal Shock Cracks)

- Due to excessive change in temperature

- Reflow, cleaning, wave solder, rework

- Inability of capacitor to relieve stresses during transient conditions.

- Maximum tensile stress occurs near end of termination

- Determined through transient thermal analyses

- Model results validated through sectioning of ceramic capacitors exposed to thermal shock conditions

- Three manifestations

- Visually detectable (rare)

- Electrically detectable

- Microcrack (worst-case)

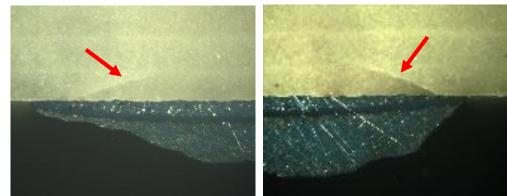

### Thermal Shock Crack: Visually Detectable

Figure 6. Severe Thermal Shock Cracks in Large MLCs

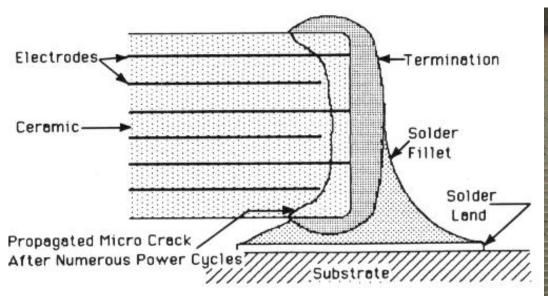

### Thermal Shock Crack: Micro Crack

- Variations in voltage or temperature will drive crack propagation

- Induces a different failure mode

- Increase in electrical resistance or decrease capacitance

### Actions: Design

- Orient terminations parallel to wave solder

- Avoid certain dimensions and materials (wave soldering)

- Maximum case size for SnPb: 1210

- Maximum case size for SAC305: 0805

- Maximum thickness: 1.2 mm

- COG, X7R preferred

- Adequate spacing from hand soldering operations

- Use manufacturer's recommended bond pad dimensions or smaller (wave soldering)

- Smaller bond pads reduce rate of thermal transfer

### Actions: Manufacturing

- Solder reflow

- Room temperature to preheat (max 2-3oC/sec)

- Preheat to at least 150oC

- Preheat to maximum temperature (max 4-5oC/sec)

- Cooling (max 2-3oC/sec)

- In conflict with profile from J-STD-020C (6oC/sec)

- Make sure assembly is less than 60oC before cleaning

- Wave soldering

- Maintain belt speeds to a maximum of 1.2 to 1.5 meters/minute

- Touch up

- Eliminate

# Module 3: Mechanisms and Physics of Failure (PoF)

## **Examples: Desired Lifetime**

- Low-End Consumer Products (Toys, etc.)

- Do they ever work?

- Cell Phones:

- Laptop Computers:

- Desktop Computers:

- Medical (External):

- Medical (Internal):

- High-End Servers:

- Industrial Controls:

- Appliances:

- Automotive:

- Avionics (Civil):

- Avionics (Military):

- Telecommunications:

- 18 to 36 months

- 24 to 36 months

- 24 to 60 months

- 5 to 10 years

- 7 years

- 7 to 10 years

- 7 to 15 years

- 7 to 15 years

- 10 to 15 years (warranty)

- 10 to 20 years

- 10 to 30 years

- 10 to 30 years

## Identify Field Environment

- Approach 1: Use of industry/military specifications

- MIL-STD-810,

- MIL-HDBK-310,

- SAE J1211,

- IPC-SM-785,

- Telcordia GR3108,

- IEC 60721-3, etc.

- Advantages

- No additional cost!

- Sometimes very comprehensive

- Agreement throughout the industry

- Missing information? Consider standards from other industries

- Disadvantages

- Most more than 20 years old

- Always less or greater than actual (by how much, unknown)

| Tmin<br>°C | Tmax                                    | AT(1)                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                       |                                                       |                                                       |                                                       |                                                       |                                                       |                                                        |

|------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|--------------------------------------------------------|

| C          | °C                                      | °C                                                                                                                                                                                                                              | t <sub>D</sub><br>hrs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Cycles/<br>year                                       | Typical<br>Years<br>of<br>Service                     | Approx.<br>Accept.<br>Failure<br>Risk, %              | Tmin<br>°C                                            | °C                                                    | ΔT <sup>(2)</sup><br>°C                               | t <sub>o</sub><br>min                                  |

| 0          | +60                                     | 35                                                                                                                                                                                                                              | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 365                                                   | 1-3                                                   | 1                                                     | +25                                                   | +100                                                  | 75                                                    | 15                                                     |

| +15        | +60                                     | 20                                                                                                                                                                                                                              | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1460                                                  | 5                                                     | 0.1                                                   | +25                                                   | +100                                                  | 75                                                    | 15                                                     |

| - 40       | +85                                     | 35                                                                                                                                                                                                                              | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 365                                                   | 7-20                                                  | 0.01                                                  | 0                                                     | +100                                                  | 100                                                   | 15                                                     |

| -55        | +95                                     | 20                                                                                                                                                                                                                              | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 365                                                   | 20                                                    | 0.001                                                 | 0                                                     | +100                                                  | 100                                                   | 15                                                     |

| -55        | +95                                     | 20<br>&40<br>&60<br>&80                                                                                                                                                                                                         | 12<br>12<br>12<br>12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 185<br>100<br>60<br>20                                | 10                                                    | 0.1                                                   | 0                                                     | +100                                                  | 100                                                   | 15                                                     |

| EE         | +05                                     | 40                                                                                                                                                                                                                              | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 100                                                   | 10                                                    | 0.1                                                   | 0                                                     |                                                       |                                                       | 15                                                     |

| -55        | . 35                                    | &60<br>&60                                                                                                                                                                                                                      | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 265                                                   | 10                                                    | 0.1                                                   | 0                                                     |                                                       |                                                       |                                                        |

| -55        | +95                                     | 3<br>to 100                                                                                                                                                                                                                     | 1<br>12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8760<br>365                                           | 5-30                                                  | 0.001                                                 | 0                                                     | +100                                                  | 100<br>& COLD <sup>(3)</sup>                          | 15                                                     |

| -55        | +95                                     | 40<br>60<br>80<br>&20                                                                                                                                                                                                           | 2<br>2<br>2<br>1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 365<br>365<br>365<br>365                              | 10                                                    | 0.01                                                  | 0                                                     | +100                                                  | 100<br>& COLD <sup>(3)</sup>                          | 15                                                     |

| -55        | +125                                    | 60<br>&100<br>&140                                                                                                                                                                                                              | 1<br>1<br>2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1000<br>300<br>40                                     | 5                                                     | 0.1                                                   | 0                                                     | +100                                                  | 100                                                   | 15                                                     |

| -          | - 40<br>-55<br>-55<br>-55<br>-55<br>-55 | +15         +60           -40         +85           -55         +95           -55         +95           -55         +95           -55         +95           -55         +95           -55         +95           -55         +95 | +15         +60         20           -40         +85         35           -55         +95         20           -55         +95         20           -55         +95         20           -55         +95         40           & 800         -55           -55         +95         3           -55         +95         3           -55         +95         40           & 800         80           -55         +95         40           60         80         80           -55         +95         60           80         820         80 | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

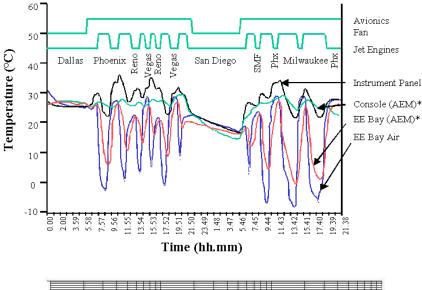

# Field Environment (continued)

- Approach 2: Based on actual measurements of similar products in similar environments

- Determine average and realistic worst-case

- Identify all failure-inducing loads

- Include <u>all</u> environments

- Manufacturing

- Transportation

- Storage

- Field

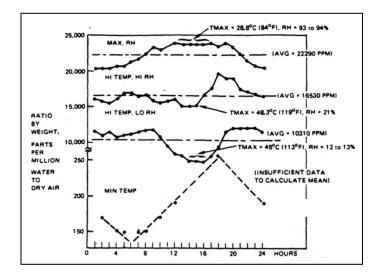

### Failure Inducing Loads

- Temperature Cycling

- Tmax, Tmin, dwell, ramp times

- Sustained Temperature

- T and exposure time

- Humidity

- Controlled, condensation

- Corrosion

- Salt, corrosive gases (Cl<sub>2</sub>, etc.)

- Power cycling

- Duty cycles, power dissipation

- Electrical Loads

- Voltage, current, current density

- Static and transient

- Electrical Noise

- Mechanical Bending (Static and Cyclic)

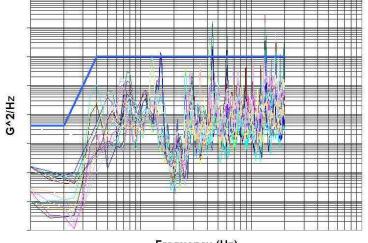

- Board-level strain

- Random Vibration

- PSD, exposure time, kurtosis

- Harmonic Vibration

- G and frequency

- Mechanical shock

- G, wave form, # of events

Frequency (Hz)

## Field Environment (Best Practice)

- Use standards when...

- Certain aspects of your environment are common

- No access to use environment

- Measure when...

- Certain aspects of your environment are unique

- Strong relationship with customer

- Do not mistake test specifications for the actual use environment

- Common mistake with vibration loads

# PoF and Wearout

- What is susceptible to long-term degradation in electronic designs?

- Ceramic Capacitors (dielectric breakdown)

- Electrolytic Capacitors (electrolyte evaporation, dielectric dissolution)

- Resistors (if improperly derated)

- Silver-Based Platings (if exposed to corrosive environments)

- Relays and other Electromechanical Components (wearout models not well developed)

- Connectors (if improperly specified and designed)

- Tin Whiskers

- Integrated Circuits (next generation feature size)

- Interconnects (Creep, Fatigue)

- Plated through holes

- Solder joints

# PoF Example: Silver and Sulfur

- Immersion silver (ImAg) introduced in the 1990's as the 'universal finish'

- Benefits

- Excellent flatness, low cost, longterm storage

- Problem

- Sulfur reacts with silver

- Induces creeping corrosion

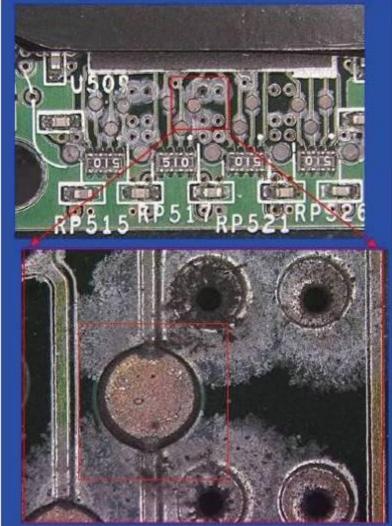

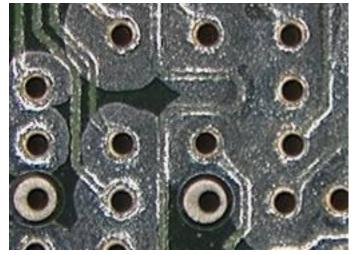

# ImAg (Creeping Corrosion)

- Failures observed within months

- Sulfur-based gases attacked exposed immersion silver

- Non-directional migration (creeping corrosion)

- Occurred primarily in environments with high sulfur levels

- Rubber manufacturing

- Gasoline refineries

- Waste treatment plants

# Findings

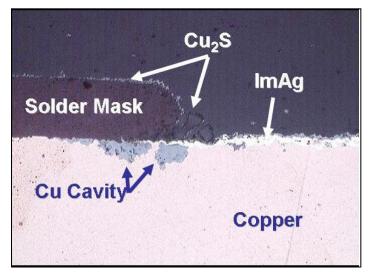

- Analysis identified copper as the creeping element (not silver)

- Cross-sections identified corrosion sites near areas with no or minimal immersion silver

- Galvanic reaction was initiating and accelerating corrosion behavior

- What went wrong?

# PoF and Testing

- Failure #1

- Test coupons were not representative of actual product

- No solder mask defined pads, no plated through holes

- Failure #2

- Industry test environments are limited to 70%RH (chamber limitations)

- Actual use environment can be more severe

| Conditions | Temp (°C) | RH (%) | H <sub>2</sub> S (ppb) | Cl <sub>2</sub> (ppb) | NO <sub>2</sub> (ppb) | SO <sub>2</sub> (ppb) |

|------------|-----------|--------|------------------------|-----------------------|-----------------------|-----------------------|

| Indoor     | 30±1      | 70±2   | 10±1.5                 | 10±1.5                | 200±30                | 100±15                |

| Outdoor    | 30±1      | 70±2   | 100±15                 | 20±3                  | 200±30                | 200±30                |

| •          |           |        |                        |                       |                       |                       |

Telcordia

## PoF and Immersion Silver

- The Final Failure?

- Acknowledging the reactivity of silver with sulfur and moving beyond 'test to spec' to truly capture potential risks

- The 'physics' was not well enough understood before the new material was released

## Alternatives to PoF

- Step 1: Rules of Thumb

- Step 2: Best Practice

Follow part selection guidelines

- Step 3: Norris-Landsberg

### Rules of Thumb (Constant Temperature)

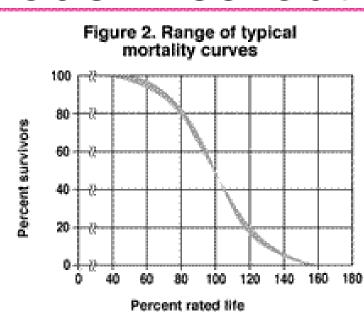

- Electrolytic Capacitor lifetime becomes an issue when ambient temperatures begin to exceed 40C on a constant basis

- 85C/2000 hour ratings tend to be insufficient for more than 5 year life

- Many companies limit solder joint temperature to a maximum of 75°C – 85°C

- Some limit IC junction temperature to a similar range

### Rules of Thumb (Temperature Cycling)

- In nominal environments, solder joint wearout is unlikely

- Low power, diurnal cycling

- $\triangle$ 25C, 1 cycle per day

- Lifetime of less than 10 years

- Greater concerns in more severe environments

- Diurnal heat sources with sufficient fluctuation ( $\Delta 40C$ )

- Diurnal power dissipation of  $\triangle 40C$  and greater

- Power cycling greater than 4 cycles/day (mini-cycling)

### Rules of Thumb (Temp Cycling)(cont.)

- If a solder joint fatigue is a concern, manage package styles

- MELF parts (SMA and SMB available)

- Crystals on ceramic substrates (especially large ones)

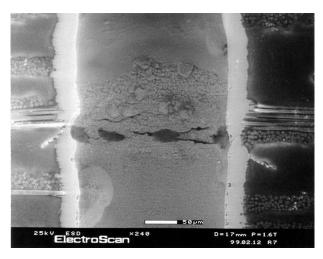

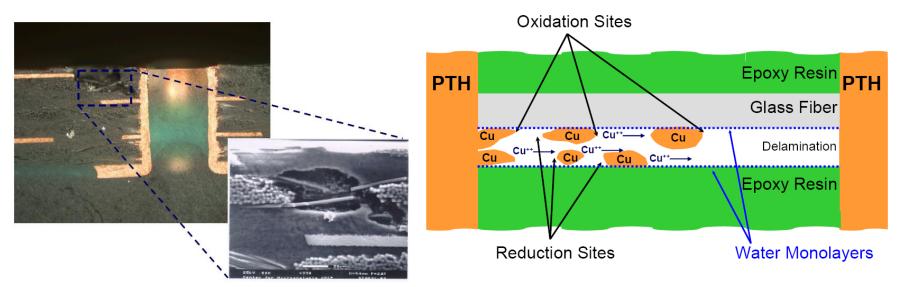

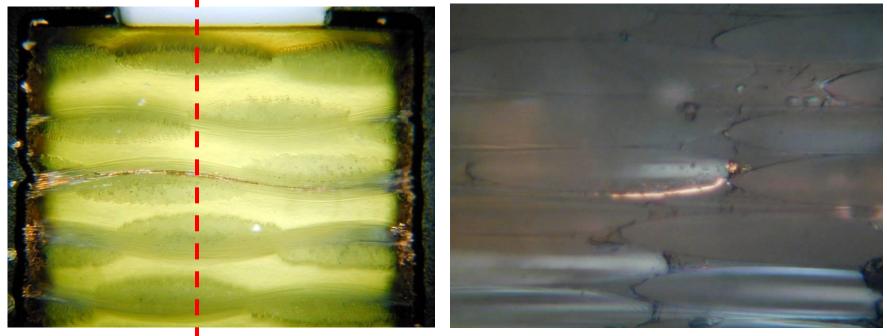

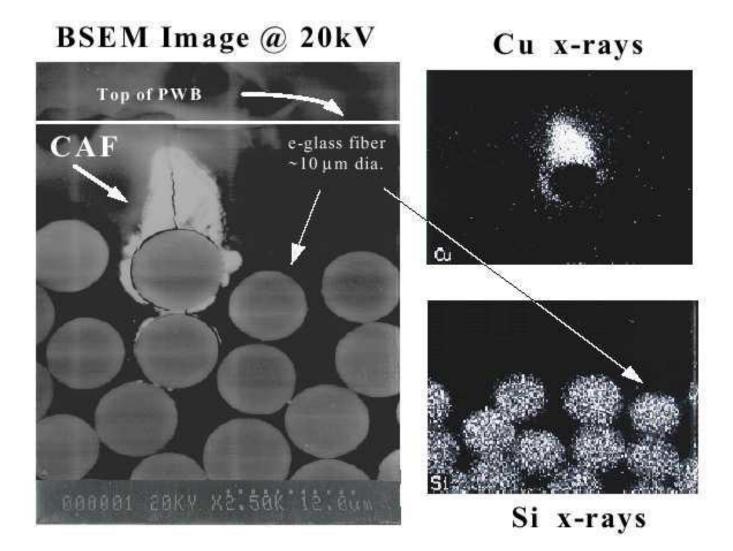

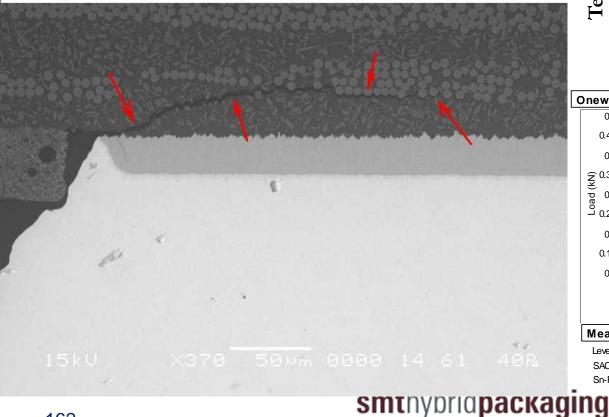

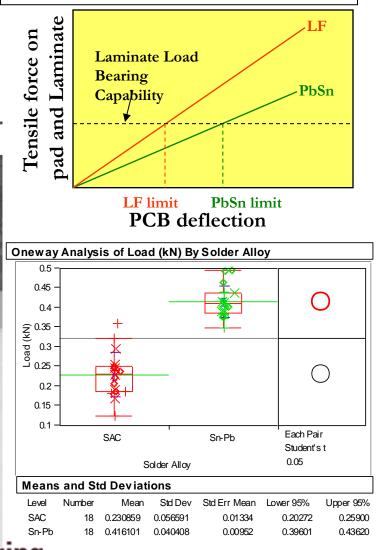

- Chip resistors greater than 1812 or capacitors greater than 2225