PCI EXPRESS<sup>®</sup> GRAPHICS-CLASS BACKPLANES

(PICMG<sup>®</sup> 1.3)

No. 87-006706-000 Revision i-G

TECHNICAL REFERENCE

### WARRANTY

The following is an abbreviated version of Trenton Technology's warranty policy for PICMG<sup>®</sup> 1.3 products. For a complete warranty statement, contact Trenton or visit our website at www.TrentonTechnology.com.

Trenton PICMG<sup>®</sup> 1.3 products are warranted against material and manufacturing defects for five years from date of delivery to the original purchaser. Buyer agrees that if this product proves defective Trenton Technology Inc. is only obligated to repair, replace or refund the purchase price of this product at Trenton Technology's discretion. The warranty is void if the product has been subjected to alteration, neglect, misuse or abuse; if any repairs have been attempted by anyone other than Trenton Technology Inc.; or if failure is caused by accident, acts of God, or other causes beyond the control of Trenton Technology Inc. Trenton Technology Inc. reserves the right to make changes or improvements in any product without incurring any obligation to similarly alter products previously purchased.

In no event shall Trenton Technology Inc. be liable for any defect in hardware or software or loss or inadequacy of data of any kind, or for any direct, indirect, incidental or consequential damages arising out of or in connection with the performance or use of the product or information provided. Trenton Technology Inc.'s liability shall in no event exceed the purchase price of the product purchased hereunder. The foregoing limitation of liability shall be equally applicable to any service provided by Trenton Technology Inc.

### **RETURN POLICY**

Products returned for repair must be accompanied by a Return Material Authorization (RMA) number, obtained from Trenton Technology prior to return. Freight on all returned items must be prepaid by the customer, and the customer is responsible for any loss or damage caused by common carrier in transit. Items will be returned from Trenton Technology via Ground, unless prior arrangements are made by the customer for an alternative shipping method

To obtain an RMA number, call us at (800) 875-6031 or (770) 287-3100. We will need the following information:

Return company address and contact Model name and model # from the label on the back of the product Serial number from the label on the back of the product Description of the failure

An RMA number will be issued. Mark the RMA number clearly on the outside of each box, include a failure report for each board and return the product(s) to our Utica, NY facility:

TRENTON Technology Inc. 1001 Broad Street Utica, NY 13501 Attn: Repair Department

Contact Trenton for our complete service and repair policy.

# TRADEMARKS

- IBM, PC/AT, VGA, EGA, OS/2 and PS/2 are trademarks or registered trademarks of International Business Machines Corp.

- Intel is a registered trademark of Intel Corporation.

- MS-DOS and Microsoft are registered trademarks of Microsoft Corp.

- PICMG, SHB Express and the PICMG logo are trademarks or registered trademarks of the PCI Industrial Computer Manufacturers Group.

- All other brand and product names may be trademarks or registered trademarks of their respective companies.

### LIABILITY DISCLAIMER

This manual is as complete and factual as possible at the time of printing; however, the information in this manual may have been updated since that time. Trenton Technology Inc. reserves the right to change the functions, features or specifications of their products at any time, without notice.

Copyright © 2008 by Trenton Technology Inc. All rights reserved.

E-mail: Support@TrentonTechnology.com

Web: www.TrentonTechnology.com

# Table of Contents

| BEFORE YOU  | U BEGIN II                                       |

|-------------|--------------------------------------------------|

| INTRODUCTI  | ON II                                            |

| PCI EXPRESS | s <sup>®</sup> LinksII                           |

| SHB AND PI  | CMG <sup>®</sup> 1.3 BACKPLANE CONFIGURATIONS II |

| OPTIONAL I/ | O CONNECTIONS II                                 |

|             | NECTION III                                      |

| +12V AUXIL  | IARY POWER CONNECTION III                        |

|             | TIONS III                                        |

|             | HOLE PATTERNS III                                |

| FOR MORE I  | NFORMATION III                                   |

| CHAPTER 1 - | BACKPLANE OVERVIEW1-1                            |

| INTRODUCTI  | ON                                               |

| MODELS      |                                                  |

| FEATURES    |                                                  |

| CHAPTER 2 - | ISA/PCI REFERENCE2-3                             |

| ISA BUS PIN | NUMBERING                                        |

|             | ASSIGNMENTS                                      |

|             | ASSIGNMENTS                                      |

|             | NAL DESCRIPTIONS                                 |

|             | S MAP*                                           |

| INTERRUPT A | ASSIGNMENTS*                                     |

|             | BUS OVERVIEW2-10                                 |

| PCI LOCAL I | BUS SIGNAL DEFINITION                            |

| PCI LOCAL I | BUS PIN NUMBERING2-12                            |

| PCI LOCAL I | BUS PIN ASSIGNMENTS2-13                          |

| PCI LOCAL I | BUS SIGNAL DESCRIPTIONS                          |

|             | PCI EXPRESS REFERENCE                            |

|             |                                                  |

|             | ON                                               |

| PCI EXPRESS | s <sup>®</sup> Links                             |

| SHB AND PI  | CMG <sup>®</sup> 1.3 BACKPLANE CONFIGURATIONS    |

| PCI EXPRESS | S EDGE CONNECTOR PIN ASSIGNMENTS                 |

| PCI EXPRESS | S SIGNALS OVERVIEW                               |

|             | NECTION                                          |

|             | LY AND SHB INTERACTION                           |

| ELECTRICAL  | CONNECTION CONFIGURATIONS                        |

| CHAPTER 4 - | GRAPHICS-CLASS BACKPLANES4-1                     |

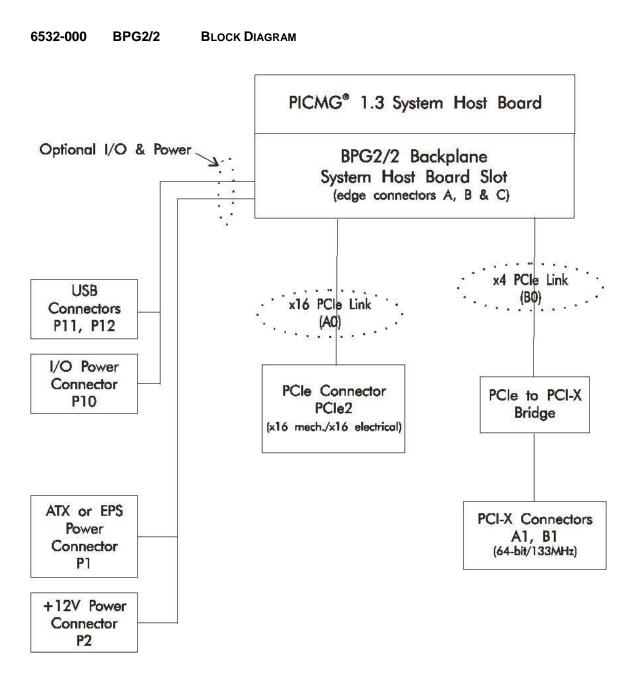

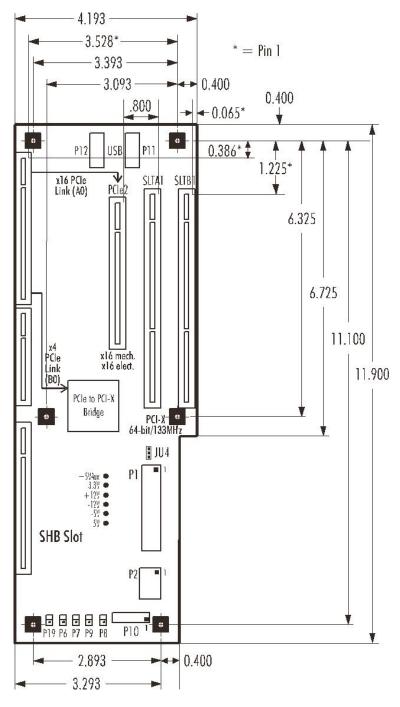

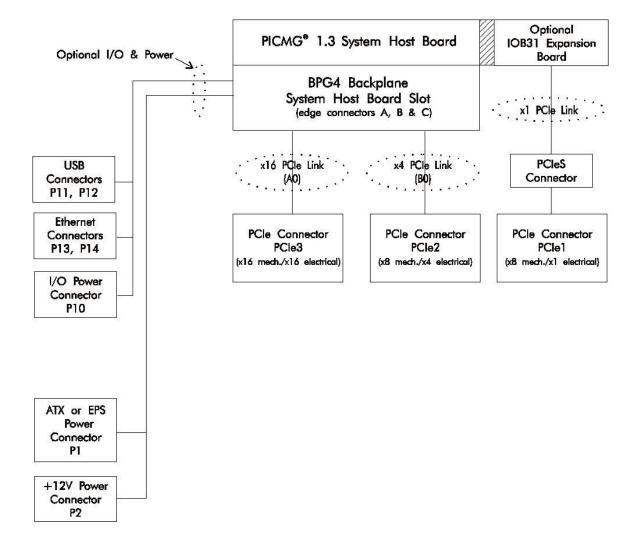

| 6532-000    | BPG2/2                                           |

| 6537-000    | BPG4                                             |

| 6544-000    | BPG65444-19                                      |

| 6600-000    | BPG66004-33                                      |

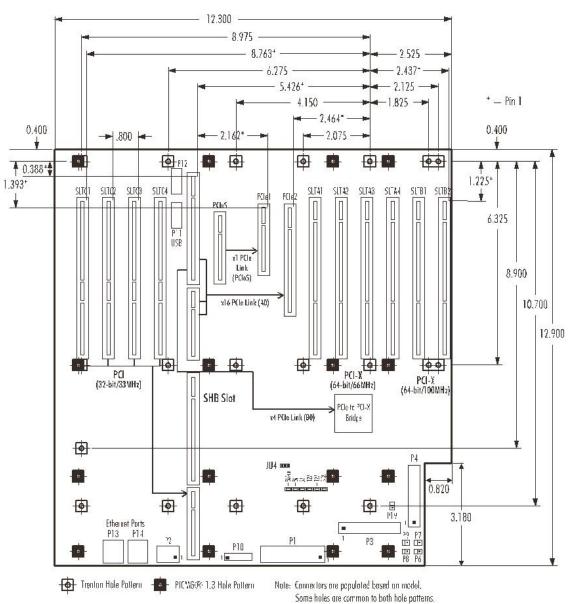

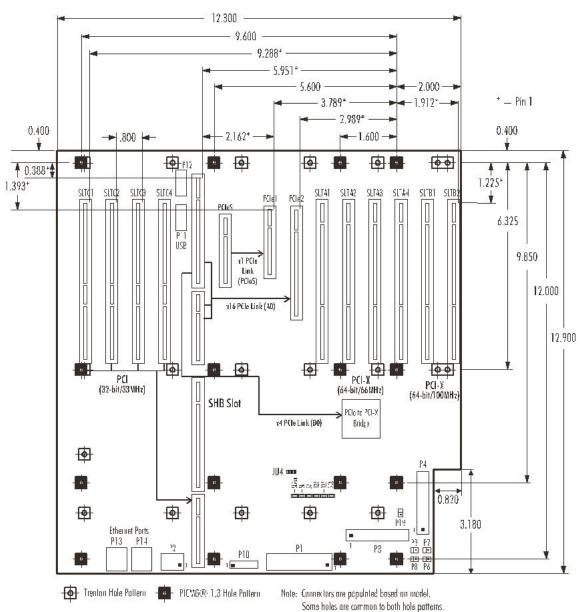

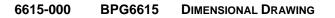

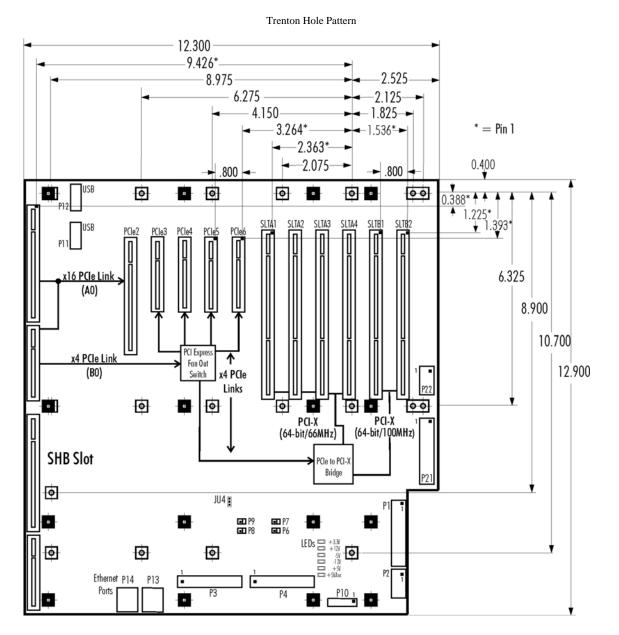

| 6615-000    | BPG66154-46                                      |

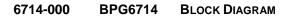

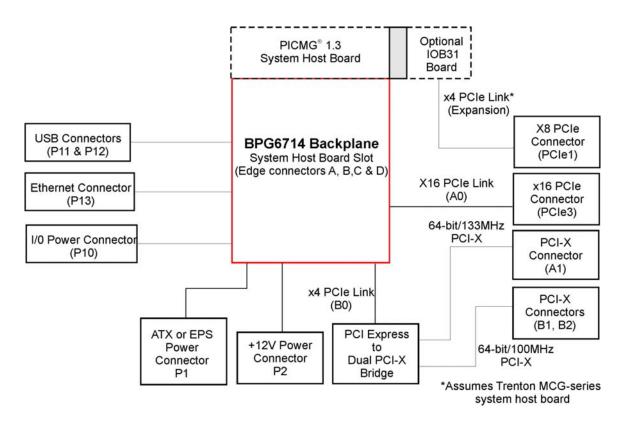

| 6714-000    | BPG67144-54                                      |

| CHAPTER 5   | MULTIPLE SHB SEGMENT BACKPLANES 5-1              |

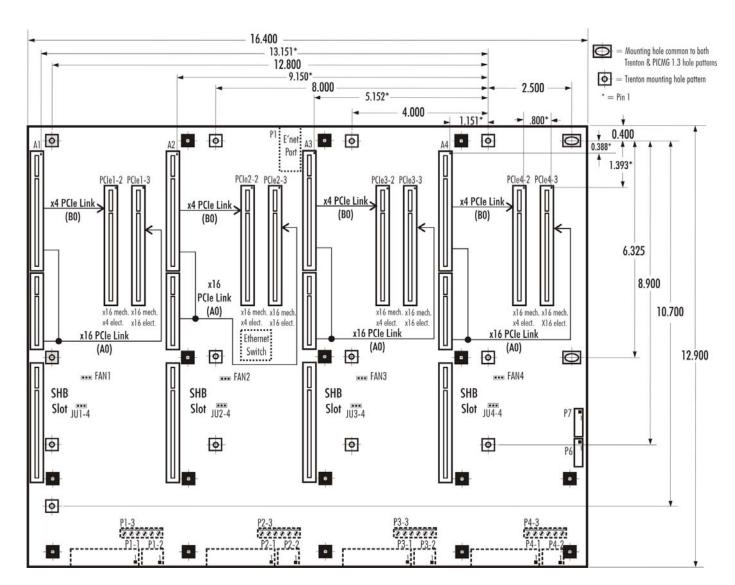

| 6605-000    | BP6FS6605                                        |

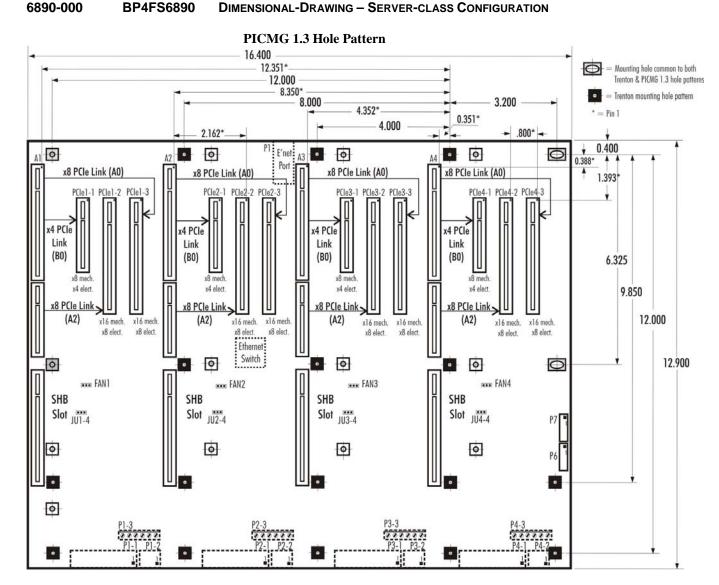

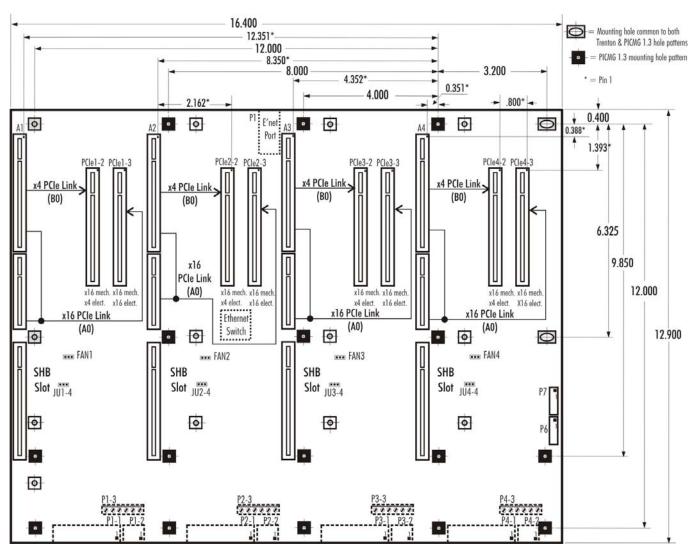

| 6890-000    | BP4FS6890                                        |

| CHAPTER 6   | 2U BUTTERFLY BACKPLANES                          |

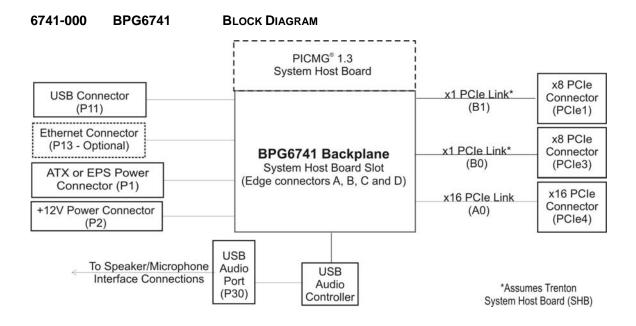

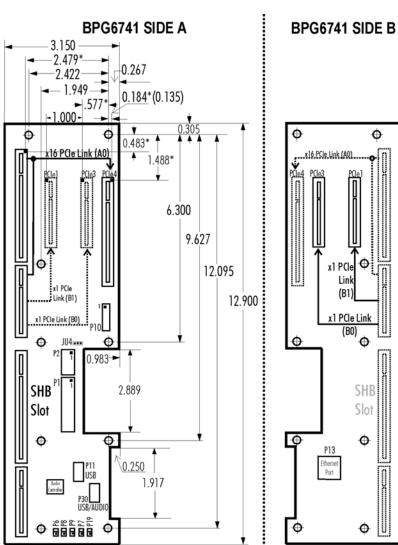

| 6741-000    | BPG67416-1                                       |

|             |                                                  |

### HANDLING PRECAUTIONS

WARNING: This product has components which may be damaged by electrostatic discharge.

To protect your backplane from electrostatic damage, be sure to observe the following precautions when handling or storing the backplane:

- Keep the backplane in its static-shielded bag until you are ready to perform your installation.

- Handle the backplane by its edges.

- Do not touch the I/O connector pins. Do not apply pressure or attach labels to the backplane.

- Use a grounded wrist strap at your workstation or ground yourself frequently by touching the metal chassis of the system before handling any components. The system must be plugged into an outlet that is connected to an earth ground.

- Use antistatic padding on all work surfaces.

- Avoid static-inducing carpeted areas.

# **Before You Begin**

# INTRODUCTION

It is important to be aware of the system considerations listed below before installing your Trenton PCI Express<sup>®</sup> backplane. Overall system performance may be affected by incorrect usage of these features.

# PCI EXPRESS<sup>®</sup> LINKS

PCI Express devices with different PCI Express link configurations can establish communication using a process called auto-negotiation or link training. If a board with a higher number of lanes is placed in a slot with a lower number of lanes (e.g., a x16 board in a x16 mechanical slot electrically configured with a x4 PCIe link) or a board with a lower number of lanes is placed into a slot with a higher number of lanes (e.g., a x4 board into a x8 slot), the PCI Express link auto-negotiates down to the lower link rate to establish communication to the system host board (SHB). The mechanical option card slots on Trenton PICMG<sup>®</sup> 1.3 backplanes have PCI Express configuration straps. Some SHB designs may utilize the straps in the PCI Express link width negotiation process.

# SHB AND PICMG® 1.3 BACKPLANE CONFIGURATIONS

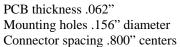

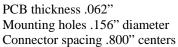

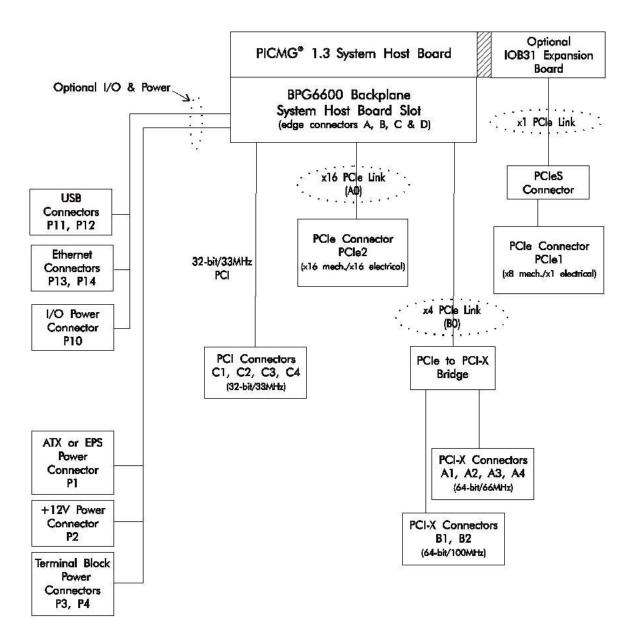

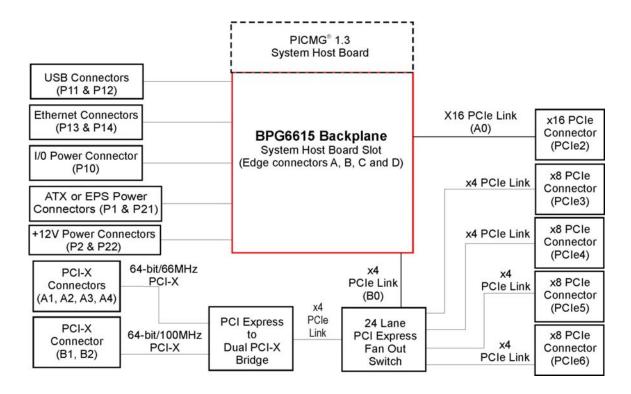

Trenton's BPG4 (6537-xxx), BPG2/2 (6532-xxx), BPG6544 (6544-xxx) and BPG6600 (6600- xxx), BPG6615 (6615- xxx), BPG6714 (6714- xxx) and BPG6741 (6741- xxx) backplanes support a graphicsclass configuration of the PCI Express links. In this type of configuration, the SHB supports one x16 PCI Express link and a single x4 link to the graphics-class backplane. These backplanes also support an additional x1 link when using Trenton's IOB31 I/O expansion board on a Trenton graphics-class SHB. The letter "G" in a Trenton backplane model name indicates a graphics-class configuration.

**NOTE:** Graphics-class SHBs should always be used with graphics-class PICMG 1.3 backplanes and server-class SHBs should always be used with server-class PICMG 1.3 backplanes. Combining incompatible SHBs and backplanes will not cause damage to the option cards or SHB, but one or more of the slots may not function and may result in one or more PCI Express option cards on the backplane being non-functional. This is due to the fact that there may not be enough available links to properly connect all of the PCI Express option card slots to the SHB.

# **OPTIONAL I/O CONNECTIONS**

The PICMG 1.3 specification enables SHB vendors to route I/O connections to edge connector C of an SHB. Trenton PICMG 1.3 backplanes support the four USB and two Ethernet connections, but since these connections are optional, not all SHBs support them. In order to take advantage of these I/O features, the SHB in your system must be able to support the connections as specified in the PCI Industrial Manufacturers Group's SHB Express<sup>TM</sup> System Host Board PCI Express Specification, PICMG<sup>®</sup> 1.3.

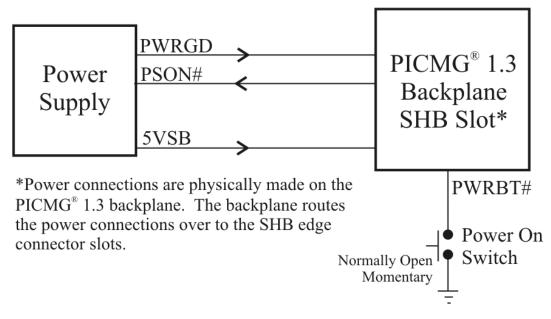

# **POWER CONNECTION**

Trenton's PCI Express backplanes support soft power control signals via the Advanced Configuration and Power Interface (ACPI) as defined in the PICMG 1.3 specification. When soft control signals are implemented, the type of ATX or EPS power supply used in the system and the operating system software will dictate how system power should be connected to the SHB. It is critical that the correct method be used.

### +12V AUXILIARY POWER CONNECTION

Trenton PICMG 1.3 backplanes provide one or more +12V power connectors for routing auxiliary power to the SHB's edge connectors, eliminating the need for auxiliary power connections on the system host board. These are 8-pin connectors that can accommodate either a 4-pin or 8-pin power cable connection.

# **POWER CAUTIONS**

**CAUTION:** Trenton recommends using EPS model power supplies with its PICMG 1.3 backplanes in systems using high-performance, dual-processor SHB Express system host boards.

The power needs of backplane option cards, high-performance processors and other system components may result in drawing 20A of current from the +12V power supply line. If this occurs, hazardous energy (240VA) could exist inside the system chassis. Final system/equipment suppliers must provide protection to service personnel from these potentially hazardous energy levels.

Standby voltages may be used in the final system design to enable certain system recovery operations. In this case, the power supply may not completely remove power to the system host board when the power switch is turned off. Caution must be taken to ensure that incoming system power is completely disconnected before removing the system host board.

In some ATX/EPS systems, the power may appear to be off while the 5VSB signal is still present and supplying power to the SHB, option cards and other system components. The +5VAUX LED on a Trenton PICMG 1.3 backplane monitors the 5VSB power signal; "green" indicates that the 5VSB signal is present. Trenton backplane LEDs monitor all DC power signals, and all of the LEDs should be off before adding or removing components. Removing boards under power may result in system damage.

# **BACKPLANE HOLE PATTERNS**

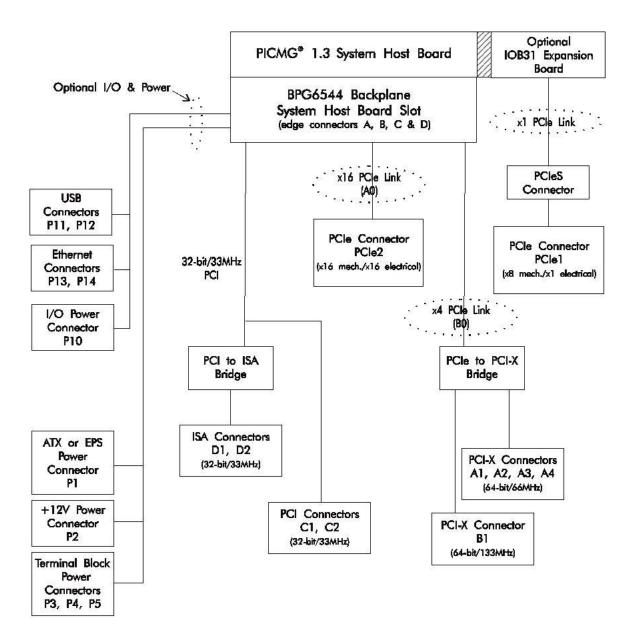

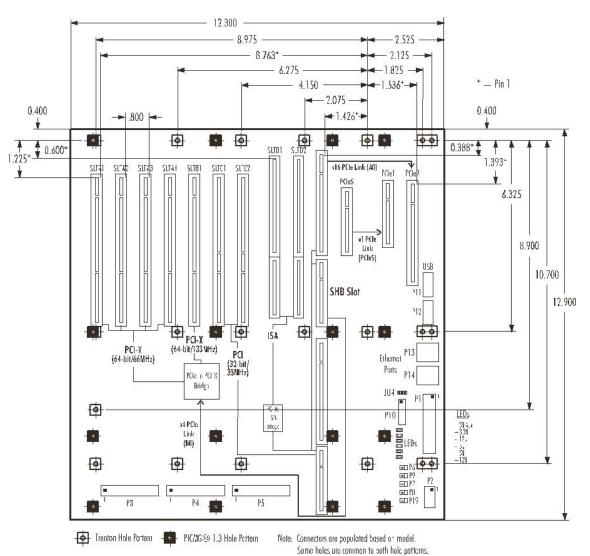

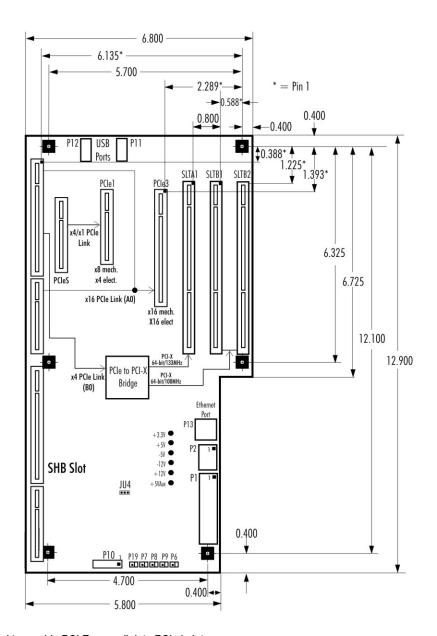

The PICMG 1.3 specification defines recommended backplane sizes and hole patterns. These hole patterns are not the same as motherboard hole patterns. Trenton's backplanes support Trenton's hole patterns for 14-slot (64-bit) and 20-slot (64-bit) backplanes as well as the hole patterns specified for PICMG 1.3 backplanes. The Trenton 14-slot hole pattern on the BPX3/8 backplane is modified slightly to accommodate the backplane's smaller width dimension. The backplane chapters in the *PCI Express*<sup>®</sup> *Graphics-class Backplanes Manual* contains mechanical dimensions and hole patterns for individual Trenton PCI Express backplanes.

# FOR MORE INFORMATION

For more information on any of these features, refer to the appropriate sections of the *PCI Express*<sup>®</sup> *Backplanes Technical Reference Manual* (#87-006706-000). The latest revision of this manual may be found on Trenton's website - www.TrentonTechnology.com.

This page intentionally left blank.

# Chapter 1 - Backplane Overview

# INTRODUCTION

Trenton PCI Express<sup>®</sup> graphics-class backplanes are six-layer or eight-layer backplanes which are PICMG<sup>®</sup> 1.3 compatible and allow the use of standard PCI Express, PCI-X, PCI or ISA option cards. Types and numbers of option cards supported vary depending on the backplane model.

Each backplane has one PCI Express<sup>®</sup> slot which accepts an SHB Express<sup>™</sup> system host board (SHB). The backplanes have a varying number of PCI Express slots available for use.

**NOTE:** On some of the backplanes, one of the PCI Express slots connects to a PCI Express expansion slot (PCIeS) on the backplane. In order to use this PCIe slot when you are using a Trenton PCI Express SHB, you must have a Trenton IOB31 (6474-000) I/O expansion board on the SHB. The IOB31 enables communication between the SHB and the PCI Express slot by providing a x1 or x4 PCI Express link to the PCIeS slot, depending on the capabilities of the SHB.

Refer to the backplane descriptions in the following chapters of this manual for more information about a specific backplane.

# MODELS

**NOTE:** In the chart below, the descriptions of the PCI Express slots include the electrical link rate of the slots, not the mechanical size.

| <u>Model #</u><br>Graphics-Class | <u>Model Name</u><br>Backplanes: | Description                                                                                                                                                                         |

|----------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6532-000                         | BPG2/2                           | 1 SHB Slot,<br>1 x16 PCI Express,<br>2 PCI-X 64-bit/133MHz                                                                                                                          |

| 6537-000                         | BPG4                             | <ol> <li>SHB Slot,</li> <li>x16 PCI Express,</li> <li>x4 PCI Express,</li> <li>x1 PCI Express via a PCIe Expansion Slot</li> </ol>                                                  |

| 6544-000                         | BPG6544                          | 1 SHB Slot,<br>1 x16 PCI Express,<br>1 z4/x1 PCI Express via a PCIe Expansion Slot,<br>1 PCI-X 64-bit/133MHz,<br>4 PCI-X 64-bit/66MHz,<br>2 PCI 32-bit/33MHz,<br>2 ISA 32-bit/33MHz |

| <u>Model #</u><br>Graphics-Class  | <u>Model Name</u><br>Backplanes: (Con | Description<br>tinued)                                                                                                                                                                            |

|-----------------------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6600-000                          | BPG6600                               | 1 SHB Slot,<br>1 x16 PCI Express,<br>1 x4/x1 PCI Express via a PCIe Expansion Slot,<br>2 PCI-X 64-bit/100MHz,<br>4 PCI-X 64-bit/66MHz,<br>4 PCI 32-bit/33MHz                                      |

| 6615-000                          | BPG6615                               | 1 SHB Slot,<br>1 x16 PCI Express,<br>4 x4 PCI Express,<br>2 PCI-X 64-bit/100MHz,<br>4 PCI-X 64-bit/66MHz                                                                                          |

| 6714-000                          | BPG6714                               | <ol> <li>SHB Slot,</li> <li>x16 PCI Express,</li> <li>x4 PCI Express,</li> <li>x4/x1 PCI Express via a PCIe Expansion Slot,</li> <li>PCI-X 64-bit/133MHz,</li> <li>PCI-X 64-bit/100MHz</li> </ol> |

| <b>Mutilple SHB-0</b><br>6605-000 | C <b>lass Backplanes</b><br>BP6FS6605 | 6 SHB Slot,<br>6 x16 PCI Express,<br>3 x4 PCI Express                                                                                                                                             |

| 2U Butterfly-Class Backplanes |         |                    |  |  |  |

|-------------------------------|---------|--------------------|--|--|--|

| 6741-000                      | BPG6741 | 1 SHB Slot,        |  |  |  |

|                               |         | 1 x16 PCI Express, |  |  |  |

### FEATURES

- Six-layer or eight-layer printed circuit board

- High noise immunity construction

- Accept system host boards (SHBs) which are PCI Industrial Computer Manufacturers Group (PICMG<sup>®</sup>) 1.3 compatible

- Allow use of standard PCI Express, PCI-X, PCI or ISA option cards, depending on model

2 x1 PCI Express

• Multiple power supply connectors, depending on model

# Chapter 2 - ISA/PCI Reference

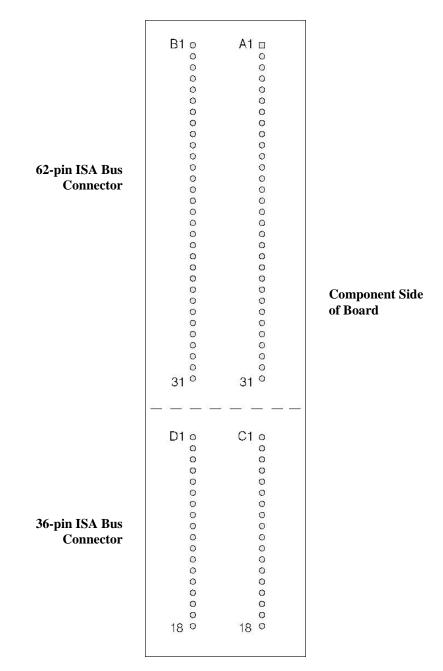

**ISA BUS PIN NUMBERING**

# **ISA BUS PIN ASSIGNMENTS**

The following tables summarize pin assignments for the Industry Standard Architecture (ISA) Bus connectors.

| I/O Pin | Signal Name | I/O | I/O Pin | Signal Name | I/O    |

|---------|-------------|-----|---------|-------------|--------|

| A1      | IOCHK#      |     | B1      | Gnd         | Ground |

| A2      | D7          | I/O | B2      | RESDRV      | 0      |

| A3      | D6          | I/O | B3      | +5V         | Power  |

| A4      | D5          | I/O | B4      | IRQ9        | I      |

| A5      | D4          | I/O | B5      | -5V         | Power  |

| A6      | D3          | I/O | B6      | DRQ2        | I      |

| A7      | D2          | I/O | B7      | -12V        | Power  |

| A8      | D1          | I/O | B8      | NOWS#       | I      |

| A9      | D0          | I/O | B9      | +12V        | Power  |

| A10     | CHRDY       | I   | B10     | Gnd         | Ground |

| A11     | AEN         | 0   | B11     | SMWTC#      | 0      |

| A12     | SA19        | I/O | B12     | SMRDC#      | 0      |

| A13     | SA18        | I/O | B13     | IOWC#       | I/O    |

| A14     | SA17        | I/O | B14     | IORC#       | I/O    |

| A15     | SA16        | I/O | B15     | DAK3#       | 0      |

| A16     | SA15        | I/O | B16     | DRQ3        | I      |

| A17     | SA14        | I/O | B17     | DAK1#       | 0      |

| A18     | SA13        | I/O | B18     | DRQ1        | 1      |

| A19     | SA12        | I/O | B19     | REFRESH#    | I/O    |

| A20     | SA11        | I/O | B20     | BCLK        | 0      |

| A21     | SA10        | I/O | B21     | IRQ7        |        |

| A22     | SA9         | I/O | B22     | IRQ6        |        |

| A23     | SA8         | I/O | B23     | IRQ5        |        |

| A24     | SA7         | I/O | B24     | IRQ4        |        |

| A25     | SA6         | I/O | B25     | IRQ3        |        |

| A26     | SA5         | I/O | B26     | DAK2#       | 0      |

| A27     | SA4         | I/O | B27     | T-C         | 0      |

| A28     | SA3         | I/O | B28     | BALE        | 0      |

| A29     | SA2         | I/O | B29     | +5V         | Power  |

| A30     | SA1         | I/O | B30     | osc         | 0      |

| A31     | SA0         | I/O | B31     | Gnd         | Ground |

| I/O Pin | Signal Name | I/O | I/O Pin | Signal Name | I/O    |

|---------|-------------|-----|---------|-------------|--------|

|         |             |     |         |             |        |

| C1      | SBHE#       | I/O | D1      | M16#        | I      |

| C2      | LA23        | I/O | D2      | IO16#       | I      |

| C3      | LA22        | I/O | D3      | IRQ10       | I      |

| C4      | LA21        | I/O | D4      | IRQ11       | I      |

| C5      | LA20        | I/O | D5      | IRQ12       | I      |

| C6      | LA19        | I/O | D6      | IRQ15       | I      |

| C7      | LA18        | I/O | D7      | IRQ14       | I      |

| C8      | LA17        | I/O | D8      | DAK0#       | 0      |

| C9      | MRDC#       | I/O | D9      | DRQ0        | I      |

| C10     | MWTC#       | I/O | D10     | DAK5#       | 0      |

| C11     | D8          | I/O | D11     | DRQ5        | I      |

| C12     | D9          | I/O | D12     | DAK6#       | 0      |

| C13     | D10         | I/O | D13     | DRQ6        | I      |

| C14     | D11         | I/O | D14     | DAK7#       | 0      |

| C15     | D12         | I/O | D15     | DRQ7        | I      |

| C16     | D13         | I/O | D16     | +5V         | Power  |

| C17     | D14         | I/O | D17     | Master16#   | I      |

| C18     | D15         | I/O | D18     | Gnd         | Ground |

# **ISA BUS SIGNAL DESCRIPTIONS**

The following is a description of the ISA Bus signals. All signal lines are TTL- compatible.

# AEN (O)

Address Enable (AEN) is used to degate the microprocessor and other devices from the I/O channel to allow DMA transfers to take place. When this line is active, the DMA controller has control of the address bus, the data-bus Read command lines (memory and I/O), and the Write command lines (memory and I/O).

# BALE (O) (Buffered)

Address Latch Enable (BALE) is provided by the bus controller and is used on the system board to latch valid addresses and memory decodes from the microprocessor. It is available to the I/O channel as an indicator of a valid microprocessor or DMA address (when used with AEN). Microprocessor addresses SA[19::0] are latched with the falling edge of BALE. BALE is forced high during DMA cycles.

# BCLK (O)

BCLK is the system clock. The clock has a 50% duty cycle. This signal should only be used for synchronization. It is not intended for uses requiring a fixed frequency.

# CHRDY (I)

I/O Channel Ready (CHRDY) is pulled low (not ready) by a memory or I/O device to lengthen I/ O or memory cycles. Any slow device using this line should drive it low immediately upon detecting its valid address and a Read or Write command. Machine cycles are extended by an integral number of clock cycles. This signal should be held low for no more than 2.5 microseconds.

# D[15::0] (I/O)

Data signals D[15::0] provide bus bits 15 through 0 for the microprocessor, memory, and I/O devices. D15 is the most-significant bit and D0 is the least-significant bit. All 8-bit devices on the I/O channel should use D[7::0] for communications to the microprocessor. The 16-bit devices will use D[15::0]. To support 8-bit devices, the data on D[15::8] will be gated to D[7::0] during 8-bit transfers to these devices. 16-bit microprocessor transfers to 8-bit devices will be converted to two 8-bit transfers.

# DAK[7::5]#, DAK[3::0]# (O)

DMA Acknowledge DAK[7::5]# and DAK[3::0]# are used to acknowledge DMA requests DRQ[7::5] and DRQ[3::0]. They are active low.

# DRQ[7::5], DRQ[3::0] (I)

DMA Requests DRQ[7::5] and DRQ[3::0] are asynchronous channel requests used by peripheral devices and the I/O channel microprocessors to gain DMA service (or control of the system). They are prioritized, with DRQ0 having the highest priority and DRQ7 having the lowest. A request is generated by bringing a DRQ line to an active level. A DRQ line must be held high until the corresponding DMA Request Acknowledge (DAK) line goes active. DRQ[3::0] will perform 8-bit DMA transfers; DRQ[7::5] will perform 16-bit transfers.

# IO16# (I)

I/O 16-bit Chip Select (IO16#) signals the system board that the present data transfer is a 16-bit, 1 waitstate, I/O cycle. It is derived from an address decode. IO16# is active low and should be driven with an open collector or tri-state driver capable of sinking 20 mAmps.

# IOCHK# (I)

I/O Channel Check (IOCHK#) provides the system board with parity (error) information about memory or devices on the I/O channel. When this signal is active, it indicates an uncorrectable system error.

### IORC# (I/O)

I/O Read (IORC#) instructs an I/O device to drive its data onto the data bus. It may be driven by the system microprocessor or DMA controller, or by a microprocessor or DMA controller resident on the I/O channel. This signal is active low.

### IOWC# (I/O)

I/O Write (IOWC#) instructs an I/O device to read the data on the data bus. It may be driven by any microprocessor or DMA controller in the system. This signal is active low.

# IRQ[15::14], IRQ[12::9], IRQ[7::3] (I)

Interrupt Requests IRQ[15::14], IRQ[12::9] and IRQ[7::3] are used to signal the microprocessor that an I/O device needs attention. The interrupt requests are prioritized, with IRQ[15::14] and IRQ[12::9] having the highest priority (IRQ9 is the highest) and IRQ[7::3] having the lowest priority (IRQ7 is the lowest). An interrupt request is generated when an IRQ line is raised from low to high. The line must be held high until the microprocessor acknowledges the interrupt request (Interrupt Service routine).

# LA[23::17] (I/O)

These signals (unlatched) are used to address memory and I/O devices within the system. They give the system up to 16MB of addressability. These signals are valid when BALE is high. LA[23::17] are not latched during microprocessor cycles and therefore do not stay valid for the whole cycle. Their purpose is to generate memory decodes for 1 wait-state memory cycles. These decodes should be latched by I/O adapters on the falling edge of BALE. These signals also may be driven by other microprocessors or DMA controllers that reside on the I/O channel.

### M16# (I)

M16# Chip Select signals the system board if the present data transfer is a 1<N>wait-state, 16- bit, memory cycle. It must be derived from the decode of LA[23::17]. M16# should be driven with an open collector or tri-state driver capable of sinking 20 mAmps.

### Master16# (I)

Master16# is used with a DRQ line to gain control of the system. A processor or DMA controller on the I/O channel may issue a DRQ to a DMA channel in cascade mode and receive a DAK#. Upon receiving the DAK#, an I/O microprocessor may pull Master16# low, which will allow it to control the system address, data, and control lines (a condition known as tri-state). After Master16# is low, the I/O microprocessor must wait one system clock period before driving the address and data lines, and two clock periods before issuing a Read or Write command. If this signal is held low for more than 15<N>microseconds, system memory may be lost because of a lack of refresh.

# NOWS# (I)

The No Wait State (NOWS#) signal tells the microprocessor that it can complete the present bus cycle without inserting any additional wait cycles. In order to run a memory cycle to a 16-bit device without wait cycles, NOWS# is derived from an address decode gated with a Read or Write command. In order to run a memory cycle to an 8-bit device with a minimum of two wait states, NOWS# should be driven active on system clock after the Read or Write command is active gated with the address decode for the device. Memory Read and Write commands to a 8-bit device are active on the falling edge of the system clock. NOWS# is active low and should be driven with an open collector or tri-state driver capable of sinking 20 mAmps.

# **OSC** (**O**)

Oscillator (OSC) is a high-speed clock with a 70-nanosecond period (14.31818 MHz). This signal is not synchronous with the system clock. It has a 50% duty cycle.

# REFRESH# (I/O)

The REFRESH# signal is used to indicate a refresh cycle and can be driven by a microprocessor on the I/O channel.

# **RESDRV** (O)

Reset Drive (RESDRV) is used to reset or initialize system logic at power-up time or during a low line-voltage outage. This signal is active high.

# SA[19::0] (I/O)

Address bits SA[19::0] are used to address memory and I/O devices within the system. These twenty address lines, in addition to LA[23::17], allow access of up to 16MB of memory. SA[19::0] are gated on the system bus when BALE is high and are latched on the falling edge of BALE. These signals are generated by the microprocessor or DMA Controller. They also may be driven by other microprocessors or DMA controllers that reside on the I/O channel.

# SBHE# (I/O)

System Bus High Enable (SBHE#) indicates a transfer of data on the upper byte of the data bus, D[15::8]. 16-bit devices use SBHE# to condition data bus buffers tied to D[15::8].

# SMRDC# (O), MRDC# (I/O)

These signals instruct the memory devices to drive data onto the data bus. SMRDC# is active only when the memory decode is within the low 1MB of memory space. MRDC# is active on all memory read cycles. MRDC# may be driven by any microprocessor or DMA controller in the system. SMRDC is derived from MRDC# and the decode of the low 1MB of memory. When a microprocessor on the I/O channel wishes to drive MRDC#, it must have the address lines valid on the bus for one system clock period before driving MRDC# active. Both signals are active low.

# SMWTC# (O), MWTC# (I/O)

These signals instruct the memory devices to store the data present on the data bus. SMWTC# is active only when the memory decode is within the low 1MB of the memory space. MWTC# is active on all memory write cycles. MWTC# may be driven by any microprocessor or DMA controller in the system. SMWTC# is derived from MWTC# and the decode of the low 1MB of memory. When a microprocessor on the I/O channel wishes to drive MWTC#, it must have the address lines valid on the bus for one system clock period before driving MWTC# active. Both signals are active low.

# **T-C** (**O**)

Terminal Count (T-C) provides a pulse when the terminal count for any DMA channel is reached.

# I/O ADDRESS MAP\*

| Hex Range | Device                                             |

|-----------|----------------------------------------------------|

| 000-01F   | DMA Controller 1                                   |

| 020-03F   | Interrupt Controller 1, Master                     |

| 040-05F   | Timer                                              |

| 060-06F   | 8042 (Keyboard)                                    |

| 070-07F   | Real-time Clock, NMI (non-maskable interrupt) Mask |

| 080-09F   | DMA Page Register                                  |

| 0A0-0BF   | Interrupt Controller 2                             |

| 0C0-0DF   | DMA Controller 2                                   |

| 0F0       | Clear Math Coprocessor Busy                        |

| 0F1       | Reset Math Coprocessor                             |

| 0F8-0FF   | Math Coprocessor                                   |

| 1F0-1F8   | Fixed Disk                                         |

| 200-207   | Game I/O                                           |

| 278-27F   | Parallel Printer Port 2                            |

| 2F8-2FF   | Serial Port 2                                      |

| 300-31F   | Prototype Card                                     |

| 360-36F   | Reserved                                           |

| 378-37F   | Parallel Printer Port 1                            |

| 380-38F   | SDLC, Bisynchronous 2                              |

| 3A0-3AF   | Bisynchronous 1                                    |

| 3B0-3BF   | Monochrome Display and Printer Adapter             |

| 3C0-3CF   | Reserved                                           |

| 3D0-3DF   | Color/Graphics Monitor Adapter                     |

| 3F0-3F7   | Diskette Controller                                |

| 3F8-3FF   | Serial Port 1                                      |

**INTERRUPT ASSIGNMENTS\***

| Interrupt | Description                           |

|-----------|---------------------------------------|

| IRQ0      | Timer Output 0                        |

| IRQ1      | Keyboard (Output Buffer Full)         |

| IRQ2      | Interrupt 8 through 15                |

| IRQ3      | Serial Port 2                         |

| IRQ4      | Serial Port 1                         |

| IRQ5      | Parallel Port 2                       |

| IRQ6      | Diskette Controller                   |

| IRQ7      | Parallel Port 1                       |

| IRQ8      | Real-time Clock Interrupt             |

| IRQ9      | Software Redirected to INT 0AH (IRQ2) |

| IRQ10     | Unassigned                            |

| IRQ11     | Unassigned                            |

| IRQ12     | Unassigned                            |

| IRQ13     | Coprocessor                           |

| IRQ14     | Fixed Disk Controller                 |

| IRQ15     | Unassigned                            |

\* These are typical parameters, which may not reflect your current system.

# PCI LOCAL BUS OVERVIEW

The PCI (Peripheral Component Interconnect) Local Bus is a high performance, 32-bit or 64-bit bus with multiplexed address and data lines. It is intended for use as an interconnect mechanism between highly integrated peripheral controller components, peripheral add-in boards and processor/memory systems.

The "local bus" moves peripheral functions with high bandwidth requirements closer to the system's processor bus and can produce substantial performance gains with graphical user interfaces (GUIs) and other high bandwidth functions (i.e., full motion video, SCSI, LANs, etc.).

The PCI Local Bus accommodates future system requirements and is applicable across multiple platforms and architectures.

The PCI component and add-in card interface is processor independent, enabling an efficient transition to future processor generations, by bridges or by direct integration, and use with multiple processor architectures. Processor independence allows the PCI Local Bus to be optimized for I/O functions, enables concurrent operation of the local bus with the processor/memory subsystem, and accommodates multiple high performance peripherals in addition to graphics. Movement to enhanced video and multimedia displays and other high bandwidth I/O will continue to increase local bus bandwidth requirements. A transparent 64-bit extension of the 32-bit data and address buses is defined, doubling the bus bandwidth and offering forward and backward compatibility of 32-bit (132MB/s peak) and 64-bit (264MB/s peak) PCI Local Bus peripherals.

# PCI LOCAL BUS SIGNAL DEFINITION

The PCI interface requires a minimum of 47 pins for a target-only device and 49 pins for a master to handle data and addressing, interface control, arbitration and system functions. The diagram below shows the pins in functional groups, with required pins on the left side and optional pins on the right side.

| <b>Required Pins:</b>                                                                                                                                                                         |                     | <b>Optional Pins:</b>                                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address & Data:<br>AD[31::00]                                                                                                                                                                 |                     | 64-bit Extension<br>AD[63::32]                                                                                                                                           |

| C/BE[3::0]#                                                                                                                                                                                   | PCI                 | C/BE[7::4]#                                                                                                                                                              |

| PAR                                                                                                                                                                                           | Compliant<br>Device | PAR64<br>REQ64#                                                                                                                                                          |

| Interface Control:<br>FRAME#<br>TRDY#<br>IRDY#<br>STOP#<br>DEVSEL#<br>IDSEL<br>Error Reporting:<br>PERR#<br>SERR#<br>Arbitration<br>(masters only):<br>REQ#<br>GNT#<br>System:<br>CLK<br>RST# |                     | ACK64#<br>Interface Control:<br>LOCK#<br>INTA#<br>INTB#<br>INTC#<br>INTD#<br>Cache Support:<br>SBO#<br>SDONE<br>JTAG (IEEE 1149.1):<br>TDI<br>TDO<br>TCK<br>TMS<br>TRST# |

|                                                                                                                                                                                               |                     |                                                                                                                                                                          |

# PCI LOCAL BUS PIN NUMBERING

| Component Side<br>of Board | B2 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0       | B1 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | A2 0 A<br>0 0<br>0 0<br>0 0<br>0 0<br>0 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 100000000000000000000000000000000000000 |

|----------------------------|------------------------------------------------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------|

|                            | 000000000000000000000000000000000000000        | 0000000000                                                                                     | 0 0 0 0 0 0 0 0                                                                   | 0 0 0 0 0 0 0 0 0 0                     |

|                            | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>61 0                                                                            | 62 ° 61                                                                           | 0 0 0 0 0                               |

5-volt/32-bit PCI Connector

Trenton Technology Inc.

### PCI LOCAL BUS PIN ASSIGNMENTS

The PCI Local Bus pin assignments shown below are for the PCI option slots on the backplane.

The PCI Local Bus specifies both 5-volt and 3.3-volt signaling environments. The following bus pin assignments are for the 5-volt connector. The 3.3-volt connector bus pin assignments are the same with the following exceptions:

- \* The pins noted as +V (I/O) are +5 volts or +3.3 volts, depending on which connector is being used.

- Pins B12, B13, A12 and A13 are Gnd (ground) on the 5-volt connector, but are Connector Keys on the 3.3-volt connector.

- †† Pin B49 is Gnd (ground) on the 5-volt connector, but is M66EN on the 3.3- volt connector.

- ††† Pins B50, B51, A50 and A51 are Connectors Keys on the 5-volt connector, but are Gnd (ground) on the 3.3-volt connector.

| I/O Pin | Signal Name | I/O Pin | Signal Name |                  |

|---------|-------------|---------|-------------|------------------|

| B1      | -12V        | A1      | TRST#       | 32-bit connector |

| B2      | ТСК         | A2      | +12V        |                  |

| B3      | Gnd         | A3      | TMS         |                  |

| B4      | TDO         | A4      | TDI         |                  |

| B5      | +5V         | A5      | +5V         |                  |

| B6      | +5V         | A6      | INTA#       |                  |

| B7      | INTB#       | A7      | INTC#       |                  |

| B8      | INTD#       | A8      | +5V         |                  |

| B9      | PRSNT1#     | A9      | Reserved    |                  |

| B10     | Reserved    | A10     | +V (I/O) *  |                  |

| B11     | PRSNT2#     | A11     | Reserved    |                  |

| B12     | Gnd         | A12     | Gnd         | 3.3-Volt Key     |

| B13     | Gnd         | A13     | Gnd         | 3.3-Volt Key     |

| B14     | Reserved    | A14     | Reserved    |                  |

| B15     | Gnd         | A15     | RST#        |                  |

| B16     | CLK         | A16     | +V (I/O) *  |                  |

| B17     | Gnd         | A17     | GNT#        |                  |

| B18     | REQ#        | A18     | Gnd         |                  |

| B19     | +V (I/O) *  | A19     | Reserved    |                  |

| B20     | AD31        | A20     | AD30        |                  |

| B21     | AD29        | A21     | +3.3V       |                  |

| B22     | Gnd         | A22     | AD28        |                  |

| B23     | AD27        | A23     | AD26        |                  |

| B24     | AD25        | A24     | Gnd         |                  |

| B25     | +3.3V       | A25     | AD24        |                  |

| B26     | C/BE3#      | A26     | IDSEL       |                  |

| B27     | AD23        | A27     | +3.3V       |                  |

| B28     | Gnd         | A28     | AD22        |                  |

| B29     | AD21        | A29     | AD20        |                  |

| B30     | AD19        | A30     | Gnd         |                  |

| B31     | +3.3V       | A31     | AD18        |                  |

| B32     | AD17        | A32     | AD16        |                  |

| B33     | C/BE2#      | A33     | +3.3V       |                  |

| B34     | Gnd         | A34     | FRAME#      |                  |

| B35     | IRDY#       | A35     | Gnd         |                  |

# PCI LOCAL BUS PIN ASSIGNMENTS (CONTINUED)

| I/O Pin | Signal Name   | I/O Pin | Signal Name   |                      |

|---------|---------------|---------|---------------|----------------------|

| B36     | +3.3V         | A36     | TRDY#         |                      |

| B37     | DEVSEL#       | A37     | Gnd           |                      |

| B38     | Gnd           | A38     | STOP#         |                      |

| B39     | LOCK#         | A39     | +3.3V         |                      |

| B40     | PERR#         | A40     | SDONE         |                      |

| B41     | +3.3V         | A41     | SBO#          |                      |

| B42     | SERR#         | A42     | Gnd           |                      |

| B43     | +3.3V         | A43     | PAR           |                      |

| B44     | C/BE1#        | A44     | AD15          |                      |

| B45     | AD14          | A45     | +3.3V         |                      |

| B46     | Gnd           | A46     | AD13          |                      |

| B47     | AD12          | A47     | AD11          |                      |

| B48     | AD10          | A48     | Gnd           |                      |

| B49     | Gnd           | A49     | AD9           |                      |

| B50     | Connector Key | A50     | Connector Key | 5-volt key           |

| B51     | Connector Key | A51     | Connector Key | 5-volt key           |

| B52     | AD8           | A52     | C/BE0#        |                      |

| B53     | AD7           | A53     | +3.3V         |                      |

| B54     | +3.3V         | A54     | AD6           |                      |

| B55     | AD5           | A55     | AD4           |                      |

| B56     | AD3           | A56     | Gnd           |                      |

| B57     | Gnd           | A57     | AD2           |                      |

| B58     | AD1           | A58     | AD0           |                      |

| B59     | +V (I/O) *    | A59     | +V (I/O) *    |                      |

| B60     | ACK64#        | A60     | REQ64#        |                      |

| B61     | +5V           | A61     | +5V           |                      |

| B62     | +5V           | A62     | +5V           | 32-bit connector end |

**PCI LOCAL BUS PIN ASSIGNMENTS (CONTINUED)** The following pin assignments apply only to backplanes with 64-bit PCI option slots.

| I/O Pin | Signal Name   | I/O Pin | Signal Name   |                        |

|---------|---------------|---------|---------------|------------------------|

|         | Connector Key |         | Connector Key | 64-bit spacer          |

|         | Connector Key |         | Connector Key | 64-bit spacer          |

| B63     | Reserved      | A63     | Gnd           | 64-bit connector start |

| B64     | Gnd           | A64     | C/BE7#        |                        |

| B65     | C/BE6#        | A65     | C/BE5#        |                        |

| B66     | C/BE4#        | A66     | +V (I/O) *    |                        |

| B67     | Gnd           | A67     | PAR64         |                        |

| B68     | AD63          | A68     | AD62          |                        |

| B69     | AD61          | A69     | Gnd           |                        |

| B70     | +V (I/O) *    | A70     | AD60          |                        |

| B71     | AD59          | A71     | AD58          |                        |

| B72     | AD57          | A72     | Gnd           |                        |

| B73     | Gnd           | A73     | AD56          |                        |

| B74     | AD55          | A74     | AD54          |                        |

| B75     | AD53          | A75     | +V (I/O) *    |                        |

| B76     | Gnd           | A76     | AD52          |                        |

| B77     | AD51          | A77     | AD50          |                        |

| B78     | AD49          | A78     | Gnd           |                        |

| B79     | +V (I/O) *    | A79     | AD48          |                        |

| B80     | AD47          | A80     | AD46          |                        |

| B81     | AD45          | A81     | Gnd           |                        |

| B82     | Gnd           | A82     | AD44          |                        |

| B83     | AD43          | A83     | AD42          |                        |

| B84     | AD41          | A84     | +V (I/O) *    |                        |

| B85     | Gnd           | A85     | AD40          |                        |

| B86     | AD39          | A86     | AD38          |                        |

| B87     | AD37          | A87     | Gnd           |                        |

| B88     | +V (I/O) *    | A88     | AD36          |                        |

| B89     | AD35          | A89     | AD34          |                        |

| B90     | AD33          | A90     | Gnd           |                        |

| B91     | Gnd           | A91     | AD32          |                        |

| B92     | Reserved      | A92     | Reserved      |                        |

| B93     | Reserved      | A93     | Gnd           |                        |

| B94     | Gnd           | A94     | Reserved      | 64-bit connector end   |

### PCI LOCAL BUS SIGNAL DESCRIPTIONS

The PCI Local Bus signals are described below and may be categorized into the following functional groups:

- System Pins

- Address and Data Pins

- Interface Control Pins

- Arbitration Pins (Bus Masters Only)

- Error Reporting Pins

- Interrupt Pins (Optional)

- Cache Support Pins (Optional)

- 64-Bit Bus Extension Pins (Optional)

- JTAG/Boundary Scan Pins (Optional)

A # symbol at the end of a signal name indicates that the active state occurs when the signal is at a low voltage. When the # symbol is absent, the signal is active at a high voltage.

The following are descriptions of the PCI Local Bus signals.

### ACK64# (optional)

Acknowledge 64-bit Transfer, when actively driven by the device that has positively decoded its address as the target of the current access, indicates the target is willing to transfer data using 64bits. ACK64# has the same timing as DEVSEL#.

### AD[31::00]

Address and Data are multiplexed on the same PCI pins. A bus transaction consists of an address phase followed by one or more data phases. During the address phase, AD[31::00] contain a physical address (32 bits). During data phases, AD[07::00] contain the least significant byte (lsb) and AD[31::24] contain the most significant byte (msb).

### AD[63::32] (optional)

Address and Data are multiplexed on the same pins and provide 32additional bits. During an address phase (when using the DAC command and when REQ64# is asserted), the upper 32bits of a 64-bit address are transferred; otherwise, these bits are reserved but are stable and indeterminate. During a data phase, an additional 32bits of data are transferred when REQ64# and ACK64# are both asserted.

### C/BE[3::0]#

Bus Command and Byte Enables are multiplexed on the same PCI pins. During the address phase of a transaction, these pins define the bus command; during the data phase they are used as byte enables. The byte enables are valid for the entire data phase and determine which byte lanes carry meaningful data. C/BE0# applies to byte0 (lsb) and C/BE3# applies to byte 3 (msb).

# C/BE[7::4]# (optional)

Bus Command and Byte Enables are multiplexed on the same pins. During an address phase (when using the DAC command and when REQ64# is asserted), the actual bus command is transferred on C/BE[7::4]#; otherwise, these bits are reserved and indeterminate. During a data phase, C/BE[7::4]# are byte enables indicating which byte lanes carry meaningful data when REQ64# and ACK64# are both asserted. C/BE4# applies to byte4 and C/BE7# applies to byte7.

### CLK

Clock provides timing for all transactions on PCI and is an input to every PCI device.

### DEVSEL#

Device Select, when actively driven, indicates that the driving device has decoded its address as the target of the current access. As an input, DEVSEL# indicates whether any device on the bus has been selected.

### FRAME#

Cycle Frame is an interface control pin which is driven by the current master to indicate the beginning and duration of an access. When FRAME# is asserted, data transfers continue; when it is deasserted, the transaction is in the final data phase.

### GNT#

Grant indicates to the agent that access to the bus has been granted. This is a point to point signal. Every master has its own GNT#.

### IDSEL

Initialization Device Select is used as a chip select during configuration read and write transactions.

### INTA#, INTB#, INTC#, INTD# (optional)

Interrupts on PCI are optional and defined as "level sensitive," asserted low (negative true), using open drain output drivers. PCI defines one interrupt for a single function and up to four interrupt lines for a multi-function device or connector.

Interrupt A is used to request an interrupt. For a single function device, only INTA# may be used, while the other three interrupt lines have no meaning.

Interrupt B, Interrupt C and Interrupt D are used to request additional interrupts and only have meaning on a multifunction device.

### IRDY#

Initiator Ready indicates the initiating agent's (bus master's) ability to complete the current data phase of the transaction. IRDY# is used in conjunction with TRDY#. During a write, IRDY# indicates that valid data is present on AD[31::0]. During a read, it indicates that the master is prepared to accept data.

### LOCK#

Lock indicates an operation that may require multiple transactions to complete. When LOCK# is asserted, nonexclusive transactions may proceed to an address that is not currently locked.

### PAR

Parity is even parity across AD[31::00] and C/BE[3::0]#. Parity generation is required by all PCI agents. The master drives PAR for address and write data phases; the target drives PAR for read data phases.

### PAR64 (optional)

Parity Upper DWORD is the even parity bit that protects AD[63::32] and C/BE[7::4]#. The master drives PAR64 for address and write data phases; the target drives PAR64 for read data phases.

### PERR#

Parity Error is for the reporting of data parity errors during all PCI transactions except a Special Cycle. There are no special conditions when a data parity error may be lost or when reporting of an error may be delayed.

### PRSNT1# and PRSNT2#

PRSNT1# and PRSNT2# are related to the connector only, not to other PCI components. They are used for two purposes: indicating that a board is physically present in the slot and providing information about the total power requirements of the board.

### REQ#

Request indicates to the arbiter that this agent desires use of the bus. This is a point to point signal. Every master has its own REQ#.

### **REQ64#** (optional)

Request 64-bit Transfer, when actively driven by the current bus master, indicates it desires to transfer data using 64 bits. REQ64# has the same timing as FRAME#. REQ64# has meaning at the end of reset.

### RST#

Reset is used to bring PCI-specific registers, sequencers and signals to a consistent state.

### SBO# (optional)

Snoop Backoff is an optional cache support pin which indicates a hit to a modified line when asserted. When SBO# is deasserted and SDONE is asserted, it indicates a "clean" snoop result.

### SDONE (optional)

Snoop Done is an optional cache support pin which indicates the status of the snoop for the current access. When deasserted, it indicates the result of the snoop is still pending. When asserted, it indicates the snoop is complete.

### SERR#

System Error is for reporting address parity errors, data parity errors on the Special Cycle command, or any other system error where the result will be catastrophic. If an agent does not want a non-maskable interrupt (NMI) to be generated, a different reporting mechanism is required.

### STOP#

Stop indicates that the current target is requesting the master to stop the current transaction.

### TCK (optional)

Test Clock is used to clock state information and test data into and out of the device during operation of the TAP (Test Access Port).

### **TDI** (optional)

Test Data Input is used to serially shift test data and test instructions into the device during TAP (Test Access Port) operation.

### **TDO** (optional)

Test Data Output is used to serially shift test data and test instructions out of the device during TAP (Test Access Port) operation.

### TMS (optional)

Test Mode Select is used to control the state of the TAP (Test Access Port) controller in the device.

### TRDY#

Target Ready indicates the target agent's (selected device's) ability to complete the current data phase of the transaction. TRDY# is used in conjunction with IRDY#. During a read, TRDY# indicates that valid data is present on AD[31::00]. During a write, it indicates that the target is prepared to accept data.

### **TRST#** (optional)

Test Reset provides an asynchronous initialization of the TAP controller. This signal is optional in the IEEE Standard Test Access Port and Boundary Scan Architecture.

This page intentionally left blank.

# Chapter 3 - PCI Express® Reference

# INTRODUCTION

PCI Express<sup>®</sup> is a high-speed, high-bandwidth interface with multiple channels (lanes) bundled together with each lane using full-duplex, serial data transfers with high clock frequencies.

The PCI Express architecture is based on the conventional PCI addressing model, but improves upon it by providing a high-performance physical interface and enhanced capabilities. Whereas the PCI bus architecture provided parallel communication between a processor board and backplane, the PCI Express protocol provides high-speed serial data transfer, which allows for higher clock speeds. The same data rate is available in both directions simultaneously, effectively reducing bottlenecks between the system host board (SHB) and PCI Express option cards.

PCI Express option cards may require updated device drivers. Most operating systems that support legacy PCI cards will also support PCI Express cards without modification. Because of this design, PCI, PCI-X and PCI Express option cards can co-exist in the same system.

PCI Express connectors have lower pin counts than PCI bus connectors. The PCIe connectors are physically different, based on the number of lanes in the connector.

# PCI EXPRESS<sup>®</sup> LINKS

Several PCI Express channels (lanes) can be bundled for each expansion slot, leaving room for stages of expansion.

A basic PCI Express lane consists of a set of differential signal pairs: one pair for transmission and one pair for reception. A PCI Express link is a collection of one or more PCIe lanes. PCI Express supports scalable link widths in 1-, 4-, 8- and 16-lane configurations, generally referred to as x1, x4, x8 and x16 slots. A x1 ("by 1") slot indicates that the slot has one PCIe lane, which gives it a bandwidth of 250MB/s in each direction. Since devices do not compete for bandwidth, the effective bandwidth, counting bandwidth in both directions, is 500MB/s (full-duplex).

The number and configuration of an SHB's PCI Express links is determined by specific component PCI Express specifications. The bandwidths for the PCIe links are determined by the link width multiplied by 250MB/s and 500MB/s, as follows:

| Slot |           | Full-Duplex |

|------|-----------|-------------|

| Size | Bandwidth | Bandwidth   |

| x1   | 250MB/s   | 500MB/s     |

| x4   | 1GB/s     | 2GB/s       |

| x8   | 2GB/s     | 4GB/s       |

| x16  | 4GB/s     | 8GB/s       |

Scalability is a core feature of PCI Express. PCI Express interface scalability enables greater system operational flexibility and efficiency.

PCI Express devices with different PCI Express link configurations can establish communication using a process called auto-negotiation or link training. If a board with a higher number of lanes is placed in a slot with a lower number of lanes (e.g., a x16 board in a x1 slot) or a board with a lower number of lanes is placed into a slot with a higher number of lanes (e.g., a x4 board into a x16 slot), the link auto-negotiates down to the lower link rate to establish communication. The mechanical option card slots on Trenton PICMG<sup>®</sup> 1.3 backplanes have PCI Express configuration straps. Some SHB designs may utilize the straps in the PCI Express link width negotiation process.

In order to properly support all of the PCI Express option card slots or devices on a PICMG 1.3 backplane, the SHB must provide an adequate number of both PCI Express links and PCI Express reference clocks.

For more information, refer to the PCI Industrial Manufacturers Group's SHB Express<sup>TM</sup> System Host Board PCI Express Specification, PICMG<sup>®</sup> 1.3.

# SHB AND PICMG<sup>®</sup> 1.3 BACKPLANE CONFIGURATIONS

The PICMG 1.3 specification enables SHB vendors to provide multiple PCI Express configuration options for edge connectors A and B of a particular SHB. These edge connectors carry the PCI Express links and reference clocks down to the SHB slot on the PICMG 1.3 backplane. The PICMG 1.3 specification states that the SHB must provide as many reference clocks as there are potential PCI Express links on the PICMG 1.3 backplane.

The potential PCI Express link configurations of an SHB fall into two main classifications: server-class and graphics-class. The specific class and PCI Express link configuration of an SHB is determined by the chipset components used on the SHB.

A graphics-class SHB configuration should provide a x16 PCI Express link down to the backplane in order to support high-end PCI Express graphics and video cards. The graphics-class SHB configuration is generally identified by one x16 PCIe link and one x4 or four x1 links to the edge connectors.

**NOTE:** Graphics-class SHBs should always be used with graphics-class PICMG 1.3 backplanes and server-class SHBs should always be used with server-class PICMG 1.3 backplanes. Combining incompatible SHBs and backplanes will not cause damage to the option cards or SHB, but one or more of the slots may not function and may result in one or more PCI Express option cards on the backplane being non-functional. This is due to the fact that there may not be enough available links to properly connect all of the PCI Express option card slots to the SHB. Precautions have been engineered into the PICMG 1.3 specification to prevent either SHB or backplane damage if this functionality mismatch occurs.

The figures below show some typical SHB and backplane combinations that would result in all of the PCI Express slots successfully establishing communication with the SHB host device.

# Graphics-Class SHB:

PCI Express<sup>™</sup> Edge Connectors A & B: One x16 and one x4 PCI Express<sup>™</sup> Link

One x16 and one x4 PCI Express™ Link with five reference clocks

X16 x4

| BP #5          | X  |

|----------------|----|

| One x16        | ΙÈ |

| nd four x1 PCI | 5  |

| Express card   | LR |

| slots          |    |

|                |    |

ar

| x16 x1 x1 x1 x1 x1<br>↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ |  |

|-------------------------------------------------------------|--|

|                                                             |  |

| SHB Slots A & B                                             |  |

BP #6 Five x1 PCI Express card slots

PCI Express link configuration straps for each PCI Express option card slot on a PICMG 1.3 backplane are required as part of the PICMG 1.3 SHB Express<sup>™</sup> specification. These configuration straps may be used to alert the SHB as to the specific link configuration expected on each PCI Express option card slot. PCI Express communication between the SHB and option card slots is successful only when there are enough available PCI Express links established between the PICMG 1.3 SHB and each PCI Express slot or device on the backplane.

For more information, refer to the PCI Industrial Manufacturers Group's SHB Express<sup>TM</sup> System Host Board PCI Express Specification, PICMG<sup>®</sup> 1.3.

# PCI EXPRESS EDGE CONNECTOR PIN ASSIGNMENTS

Trenton PCI Express server-class backplanes provide edge connectors A, B and C.

Optional I/O signals are defined in the PICMG 1.3 specification and if implemented must be located on edge connector C of the SHB. Trenton PICMG 1.3 backplanes enable some or all of the USB and Ethernet connections on edge connector C, but since these connections are optional, not all SHBs support them. In order to take advantage of these I/O features, the SHB in your system must be able to support the connections as specified in the PCI Industrial Manufacturers Group's SHB Express<sup>TM</sup> System Host Board PCI Express Specification, PICMG<sup>®</sup> 1.3.

The BPG6544 supports two ISA slots via a PCI-to-ISA bridge chip. Since the ISA bus interface is not part of the PICMG 1.3 specification, two reserved pins are used to route the ISA signals SERIRQ and NOGO\_ISA to the backplane's PCI-to-ISA bridge chip. Legacy PCI card support is not impacted by this ISA bus signal routing requirement. The following bus pin assignments are used:

- \* SERIRQ -- connector A, pin B77

- \*\* NOGO\_ISA -- connector B, pin A2

The following table shows pin assignments for the PCI Express edge connectors on Trenton backplanes. Connector D is only available on graphics-class backplanes.

|    | Connector A    |        | Connector B |          |         | Connector C |          |         | *Connector D |          |        |

|----|----------------|--------|-------------|----------|---------|-------------|----------|---------|--------------|----------|--------|

|    | Side B         | Side A |             | Side B   | Side A  |             | Side B   | Side A  |              | Side B   | Side A |

| 1  | SMCLK          | SMDAT  | 1           | +5Vaux   | +5Vaux  | 1           | USB0P    | GND     | 1            | INTB#    | INTA#  |

| 2  | GND            | GND    | 2           | GND      | RSVD ** | 2           | USB0N    | GND     | 2            | INTD#    | INTC#  |

| 3  | TDI            | TCK    | 3           | a_PETp8  | GND     | 3           | GND      | USB1P   | 3            | GND      | VIO    |

| 4  | TDO            | TMS    | 4           | a_PETn8  | GND     | 4           | GND      | USB1N   | 4            | REQ3#    | GNT3#  |

| 5  | TRST#          | WAKE#  | 5           | GND      | a_PERp8 | 5           | USB2P    | GND     | 5            | REQ2#    | GNT2#  |

| 6  | PWRBT#         | PME#   | 6           | GND      | a_PERn8 | 6           | USB2N    | GND     | 6            | PCI_RST# | GNT1#  |

| 7  | PWRGD          | PSON#  | 7           | a_PETp9  | GND     | 7           | GND      | USB3P   | 7            | REQ1#    | GNT0#  |

| 8  | SHB_RST#       | PERST# | 8           | a_PETn9  | GND     | 8           | GND      | USB3N   | 8            | REQ0#    | SERR#  |

| 9  | CFG0           | CFG1   | 9           | GND      | a_PERp9 | 9           | USBOC0#  | GND     | 9            | SDONE    | +3.3V  |

| 10 | CFG2           | CFG3   | 10          | GND      | a_PERn9 | 10          | GND      | USBOC1# | 10           | GND      | CLKF1  |

| 11 | RSVD           | GND    | 11          | RSVD     | GND     | 11          | USBOC2#  | GND     | 11           | CLKFO    | GND    |

|    | Mechanical Key |        |             | Mechanie | cal Key |             | Mechanic | al Key  |              | Mechanic | al Key |

\* Graphics-class backplanes only.

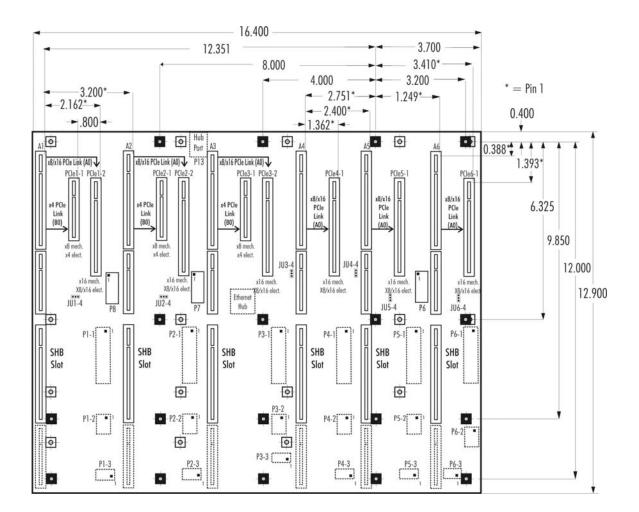

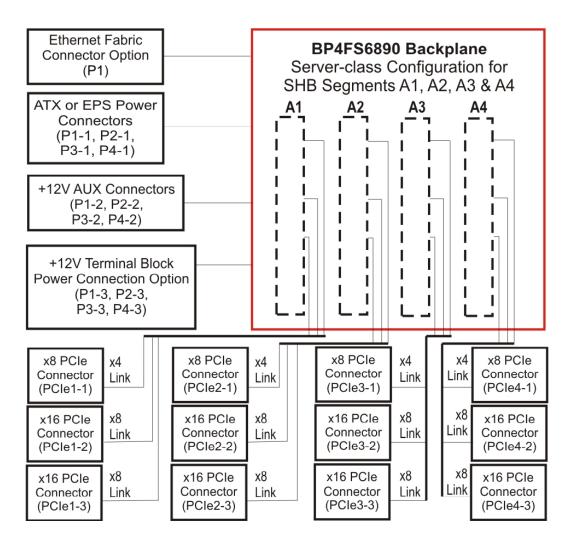

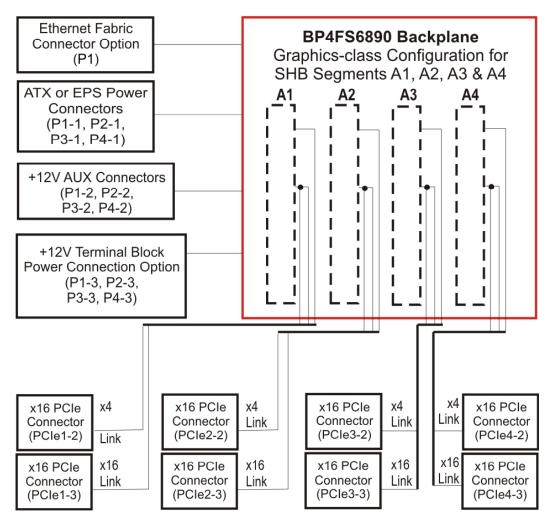

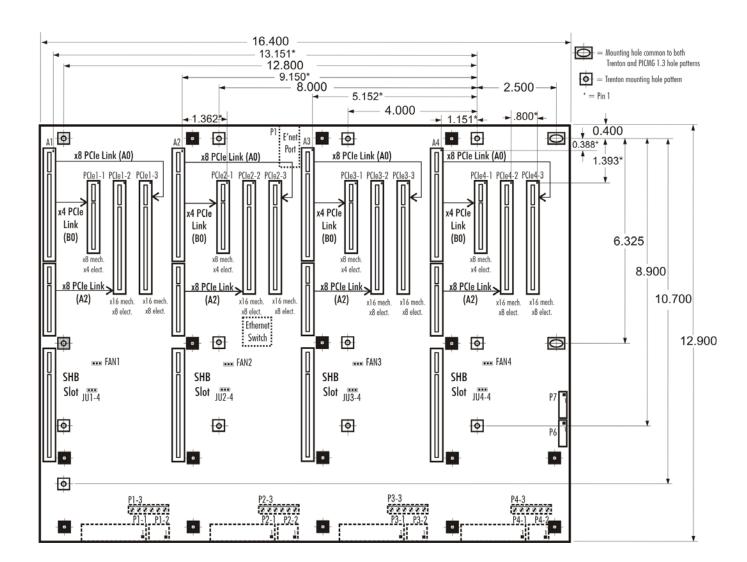

|                                                                                                | Connector A                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Connector B                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                         | Connector C                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                               | *Connector D                                                                       |                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                      |