### **MCX Series**

6633-xxx - MCXT

6685-xxx - MCXT-E

6638-xxx - MCXI

6700-xxx - MCXI-E

No. 87-006636-000 Revision D

### **TECHNICAL REFERENCE**

Intel<sup>®</sup> Dual-Core Xeon<sup>®</sup>

Intel<sup>®</sup> Quad-Core Xeon<sup>®</sup>

PROCESSOR-BASED

**Server-Class SHB**

#### WARRANTY

The following is an abbreviated version of Trenton Technology's warranty policy for PICMG® 1.3 products. For a complete warranty statement, contact Trenton or visit our website at www.TrentonTechnology.com.

Trenton PICMG® 1.3 products are warranted against material and manufacturing defects for five years from date of delivery to the original purchaser. Buyer agrees that if this product proves defective Trenton Technology Inc. is only obligated to repair, replace or refund the purchase price of this product at Trenton Technology's discretion. The warranty is void if the product has been subjected to alteration, neglect, misuse or abuse; if any repairs have been attempted by anyone other than Trenton Technology Inc.; or if failure is caused by accident, acts of God, or other causes beyond the control of Trenton Technology Inc. Trenton Technology Inc. reserves the right to make changes or improvements in any product without incurring any obligation to similarly alter products previously purchased.

In no event shall Trenton Technology Inc. be liable for any defect in hardware or software or loss or inadequacy of data of any kind, or for any direct, indirect, incidental or consequential damages arising out of or in connection with the performance or use of the product or information provided. Trenton Technology Inc.'s liability shall in no event exceed the purchase price of the product purchased hereunder. The foregoing limitation of liability shall be equally applicable to any service provided by Trenton Technology Inc.

#### **RETURN POLICY**

Products returned for repair must be accompanied by a Return Material Authorization (RMA) number, obtained from Trenton Technology prior to return. Freight on all returned items must be prepaid by the customer, and the customer is responsible for any loss or damage caused by common carrier in transit. Items will be returned from Trenton Technology via Ground, unless prior arrangements are made by the customer for an alternative shipping method

To obtain an RMA number, call us at (800) 875-6031 or (770) 287-3100. We will need the following information:

Return company address and contact Model name and model # from the label on the back of the product Serial number from the label on the back of the product Description of the failure

An RMA number will be issued. Mark the RMA number clearly on the outside of each box, include a failure report for each board and return the product(s) to our Utica, NY facility:

TRENTON Technology Inc. 1001 Broad Street Utica, NY 13501 Attn: Repair Department

Contact Trenton for our complete service and repair policy.

#### **TRADEMARKS**

IBM, PC, VGA, EGA, OS/2 and PS/2 are trademarks or registered trademarks of International Business Machines Corp.

AMI and AMIBIOS are trademarks of American Megatrends Inc.

Intel and Xeon are registered trademarks of Intel Corporation.

ATI is a registered trademark of ATI Technologies Incorporated.

MS-DOS and Microsoft are registered trademarks of Microsoft Corp.

PICMG, SHB Express and the PICMG and SHB Express logos are trademarks of the PCI Industrial Computer Manufacturers Group.

All other brand and product names may be trademarks or registered trademarks of their respective companies.

#### LIABILITY DISCLAIMER

This manual is as complete and factual as possible at the time of printing; however, the information in this manual may have been updated since that time. Trenton Technology Inc. reserves the right to change the functions, features or specifications of their products at any time, without notice.

Copyright © 2007 by Trenton Technology Inc. All rights reserved.

E-mail: Support@TrentonTechnology.com Web: www.TrentonTechnology.com

### Before You Begin

#### INTRODUCTION

It is important to be aware of the system considerations listed below before installing your MCXT (6633-xxx), MCXT-E (6685-xxx), MCXI (6638-xxx) or MCXI-E (6700-xxx) SHB. Overall system performance may be affected by incorrect usage of these features.

# PS/2 REQUIREMENTS DURING BOOT-UP

Certain operating systems require a PS/2 keyboard during boot-up. Since the SHB itself does not have a PS/2 keyboard connector, you may need Trenton's IOB30MC (6391-001) or IOB31 (6474-000) I/O board in your system to provide this functionality. If your operating system is not included below, contact Trenton for the latest information regarding IOB30MC/IOB31 requirements.

Trenton has determined that an IOB30MC or IOB31 *is* required when using the following operating systems: RedHat Enterprise Linux (RHEL) V4.0 ES 64-bit and 32-bit; QNX Neutrino 6.3.0; Fedora Core 6.0 64-bit and 32-bit; SUSE Linux 9.0 Linux Enterprise Server 64-bit and 32-bit; Sun® Solaris  $^{\text{IM}}$  10.0. An IOB30MC or IOB31 is *not* required when using the following operating systems: Microsoft® Windows® Vista 64-bit and 32-bit; Microsoft® Windows® 2000; Microsoft® Windows® XP 64-bit and 32-bit; Microsoft® Windows® 2003 Server 64-bit and 32-bit.

#### VIDEO START-UP

The first video display image could be delayed 10-30 seconds while the MCX-series SHB performs start-up diagnostics and advanced technology sequencing during system power-up. Post-code LEDs on the SHB provide a visual indication of normal board operation. The specific length of this delay depends on the amount of installed system memory and the overall system configuration.

#### **DDR2 Memory**

The 240-pin DDR2 memory modules used on the SHB must be industry standard 72-bit wide ECC registered memory modules. The FB-DIMMs must be PC2-4200 or PC2-5300 (DDR2-533 or DDR2-667) and comply with the JEDEC Rev. 2.0 specifications.

**NOTE:** All memory modules must have gold contacts.

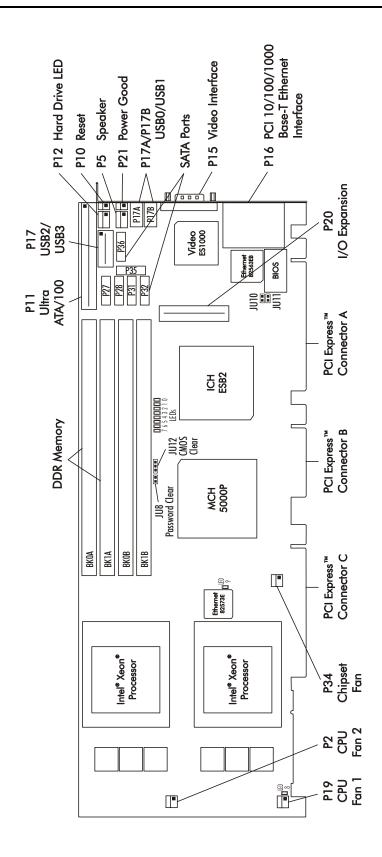

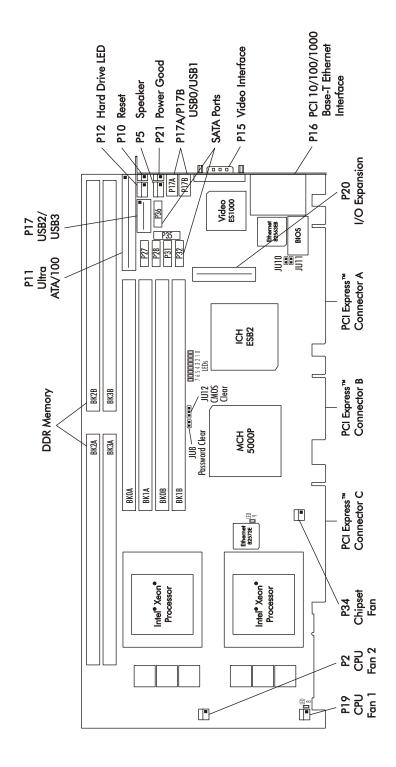

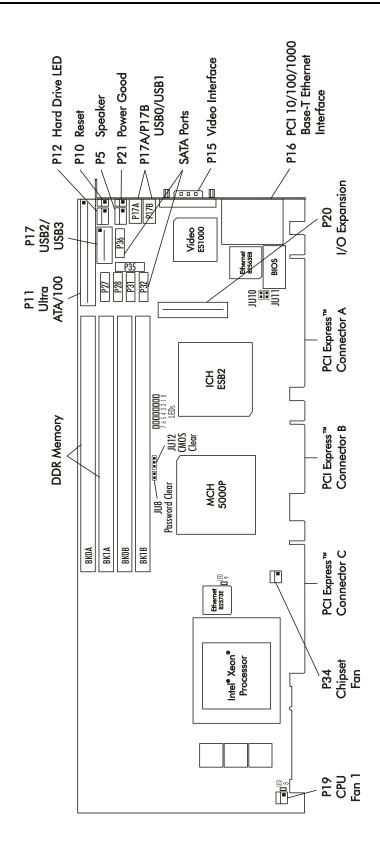

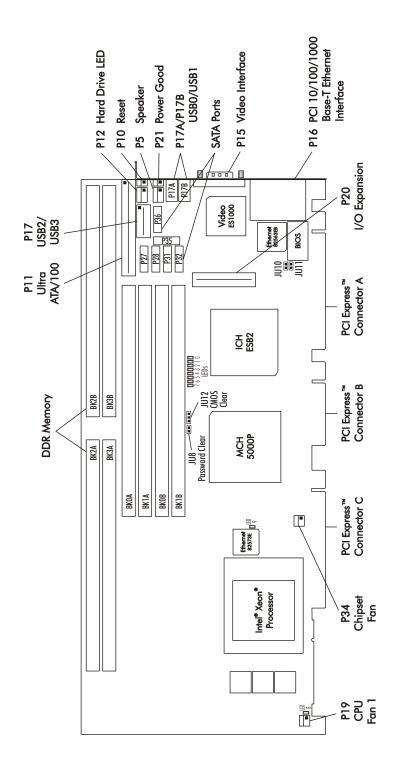

With the bracket end of the board to the right, the four FB-DIMM sockets available on the MCXT and MCXI SHBs are numbered BK0A, BK1A, BK0B and BK1B, from top to bottom. On the extended-memory MCXT-E and MCXI-E SHBs, there are an additional four FB-DIMM sockets. The upper sockets are BK2A and BK2B, from left to right, and the lower sockets are BK3A and BK3B. These socket definitions are illustrated in the board layouts in the *Specifications* chapter of the MCXT/MCXI manual.

A minimum of one 512MB FB-DIMM is required and must be populated in DIMM socket BK0A. When using more than one FB-DIMM, the memory sockets must be populated in multiples of two in order to maximize the speed and performance of the memory interface. To take full advantage of the four-channel memory interface of the SHB's memory controller hub, the FB-DIMMs in sockets BK0A and BK1A must be identical in manufacturing, speed, timing and organization. FB-DIMMs in sockets BK0B and BK1B must also be identical. FB-DIMMs in sockets contained within the same memory channel (e.g., BK0A and BK2A) do not have to be identical.

The FB-DIMMs must be installed in the SHB's FB-DIMM sockets using prescribed population rules to ensure proper memory interface operation and performance. Refer to the DDR2 Memory section of the *Specifications* chapter of the MCXT/MCXI manual for more details.

#### **POWER SUPPLY**

The MCX-series SHB requires a power supply with a minimum of 450 watts. If the power supply does not provide a minimum of 2.0 Amps of 5-volt standby current *and* 18.0 Amps of +12V current, the system may not boot. Ensure that the system supply can safely deliver adequate power to meet all remaining system requirements.

The default system shutdown option is set to **Manual Shutdown**. This prompts a shutdown screen after the operating system shuts down, which requires a manual power off in A/C power. To automatically shut down the SHB after operating system shutdown, change **Manual Shutdown** to **Auto**. This puts the SHB in S5 power-off state and does not require that a manual power off be done in order to keep the SHB off.

A/C power should always be powered off when any parts are being removed from or connected to the SHB or backplane. Failure to do so may result in serious damage to the SHB or backplane.

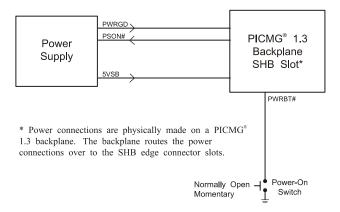

## POWER CONNECTION

The PICMG<sup>®</sup> 1.3 specification supports soft power control signals via the Advanced Configuration and Power Interface (ACPI). The MCX-series SHBs support these signals, which are controlled by the ACPI and are used to implement various sleep modes. When soft control signals are implemented, the type of ATX or EPS power supply used in the system and the operating system software will dictate how system power should be connected to the SHB. It is critical that the correct method be used. Refer to *Appendix B - Power Connection* in the MCXT/MCXI manual to determine the method that will work best for a specific system design.

#### **SATA PORTS**

SATA ports 0, 1, 2 and 3 are accessible in IDE mode. Ports 4 and 5 are only accessible when either AHCI or RAID configurations have been enabled. Your operating system may need a driver in order to install SATA in AHCI or RAID configurations. Once these configurations have been enabled, all six SATA ports are fully accessible.

# MOUSE/KEYBOARD "Y" CABLE

If you have an IOB30MC I/O board in your system and you are using a "Y" cable attached to the bracket mounted mouse/keyboard mini Din connector, be sure to use Trenton's "Y" cable, part number 5886-000. Using a non-Trenton cable may result in improper SHB operation.

# FOR MORE INFORMATION

For more information on any of these features, refer to the appropriate sections of the *MCXT/MCXI Technical Reference Manual* (#87-006636-000). The latest revision of this manual may be found on Trenton's website - www.TrentonTechnology.com. Copyright 2007 by Trenton Technology Inc. All rights reserved.

### Table of Contents

| Specifications1-1                    |

|--------------------------------------|

| Introduction1-1                      |

| Models                               |

| Features                             |

| MCX Series Block Diagram             |

| MCXT (506633-xxx) Board Layout       |

| MCXT-E (506685-xxx) Board Layout1-11 |

| MCXI (506638-xxx) Board Layout       |

| MCXI-E (506700-xxx) Board Layout     |

| Processors1-14                       |

| Bus Interfaces                       |

| Data Path                            |

| Bus Speeds                           |

| Bus Speed - System                   |

| Memory Interface                     |

| System Bus1-14                       |

| DMA Channels1-14                     |

| Interrupts1-14                       |

| BIOS (Flash)                         |

| Cache Memory                         |

| DDR2 Memory1-15                      |

| Error Checking and Correction1-16    |

| Bus Interfaces                       |

| Universal Serial Bus (USB)           |

| Super XGA Video Interface            |

| Ethernet Interfaces                  |

| Serial ATA/300 Ports                 |

| Enhanced IDE Interface               |

| Battery                              |

| Power Requirements                   |

| Power Supply                         |

| Temperature/Environment              |

| UL Recognition                       |

| Configuration Jumpers                |

| Ethernet LEDs and Connectors         |

| Status LEDs                          |

| System BIOS Setup Utility1-21        |

| Connectors 1-23                      |

### Table of Contents

| PCI Express <sup>TM</sup> Reference                                                                                                                                                                                                                                                                                                                                                                             |                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| Introduction                                                                                                                                                                                                                                                                                                                                                                                                    | 2-1                                               |

| PCI Express Links                                                                                                                                                                                                                                                                                                                                                                                               |                                                   |

| SHB Configurations                                                                                                                                                                                                                                                                                                                                                                                              | 2-2                                               |

| PCI Express Edge Connector Pin Assignments                                                                                                                                                                                                                                                                                                                                                                      | 2-3                                               |

| PCI Express Signals Overview.                                                                                                                                                                                                                                                                                                                                                                                   | 2-5                                               |

| System BIOS                                                                                                                                                                                                                                                                                                                                                                                                     | 3-1                                               |

| BIOS Operation                                                                                                                                                                                                                                                                                                                                                                                                  | 3-1                                               |

| Running AMIBIOS Setup                                                                                                                                                                                                                                                                                                                                                                                           | 3-5                                               |

| BIOS Setup Utility Main Menu                                                                                                                                                                                                                                                                                                                                                                                    | 3-6                                               |

| BIOS Setup Utility Options                                                                                                                                                                                                                                                                                                                                                                                      |                                                   |

| Security Setup                                                                                                                                                                                                                                                                                                                                                                                                  |                                                   |

| Change Supervisor Password                                                                                                                                                                                                                                                                                                                                                                                      |                                                   |

| Disabling Supervisor Password                                                                                                                                                                                                                                                                                                                                                                                   |                                                   |

| Change & Clear User Password                                                                                                                                                                                                                                                                                                                                                                                    |                                                   |

| Boot Sector Virus Protection                                                                                                                                                                                                                                                                                                                                                                                    |                                                   |

| Exit Menu & Options                                                                                                                                                                                                                                                                                                                                                                                             |                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                   |

| Advanced BIOS Setup                                                                                                                                                                                                                                                                                                                                                                                             | 4-1                                               |

| Advanced BIOS Setup                                                                                                                                                                                                                                                                                                                                                                                             |                                                   |

| •                                                                                                                                                                                                                                                                                                                                                                                                               | 4-1                                               |

| Advanced Setup Options                                                                                                                                                                                                                                                                                                                                                                                          | 4-1                                               |

| Advanced Setup Options                                                                                                                                                                                                                                                                                                                                                                                          | 4-1<br>4-5<br>4-7                                 |

| Advanced Setup Options                                                                                                                                                                                                                                                                                                                                                                                          | 4-1<br>4-5<br>4-7<br>4-11                         |

| Advanced Setup Options  CPU Configuration Setup & Options  IDE Configuration Setup & Options  IDE Device Setup Setup & Options                                                                                                                                                                                                                                                                                  | 4-1<br>4-5<br>4-7<br>4-11<br>4-15                 |

| Advanced Setup Options  CPU Configuration Setup & Options  IDE Configuration Setup & Options  IDE Device Setup Setup & Options  Floppy Configuration Setup & Options                                                                                                                                                                                                                                            | 4-1<br>4-5<br>4-7<br>4-11<br>4-15                 |

| Advanced Setup Options  CPU Configuration Setup & Options  IDE Configuration Setup & Options  IDE Device Setup Setup & Options  Floppy Configuration Setup & Options  SuperIO Configuration Setup & Options                                                                                                                                                                                                     | 4-1<br>4-5<br>4-7<br>4-15<br>4-17<br>4-21         |

| Advanced Setup Options  CPU Configuration Setup & Options  IDE Configuration Setup & Options  IDE Device Setup Setup & Options  Floppy Configuration Setup & Options  SuperIO Configuration Setup & Options  ACPI Configuration                                                                                                                                                                                 | 4-1<br>4-5<br>4-7<br>4-11<br>4-15<br>4-17<br>4-21 |

| Advanced Setup Options  CPU Configuration Setup & Options  IDE Configuration Setup & Options  IDE Device Setup Setup & Options  Floppy Configuration Setup & Options  SuperIO Configuration Setup & Options  ACPI Configuration  Advanced ACPI Configuration & Options                                                                                                                                          |                                                   |

| Advanced Setup Options  CPU Configuration Setup & Options  IDE Configuration Setup & Options  IDE Device Setup Setup & Options  Floppy Configuration Setup & Options  SuperIO Configuration Setup & Options  ACPI Configuration  Advanced ACPI Configuration & Options  Chipset ACPI Configuration and Options                                                                                                  |                                                   |

| Advanced Setup Options  CPU Configuration Setup & Options  IDE Configuration Setup & Options  IDE Device Setup Setup & Options  Floppy Configuration Setup & Options  SuperIO Configuration Setup & Options  ACPI Configuration  Advanced ACPI Configuration & Options  Chipset ACPI Configuration and Options  AHCI Configuration                                                                              |                                                   |

| Advanced Setup Options  CPU Configuration Setup & Options  IDE Configuration Setup & Options  IDE Device Setup Setup & Options  Floppy Configuration Setup & Options  SuperIO Configuration Setup & Options  ACPI Configuration  Advanced ACPI Configuration & Options  Chipset ACPI Configuration and Options  AHCI Configuration  AHCI Port 0                                                                 |                                                   |

| Advanced Setup Options  CPU Configuration Setup & Options  IDE Configuration Setup & Options  IDE Device Setup Setup & Options  Floppy Configuration Setup & Options  SuperIO Configuration Setup & Options  ACPI Configuration  Advanced ACPI Configuration & Options  Chipset ACPI Configuration and Options  AHCI Configuration  AHCI Port 0  MPS Configuration Setup & Options  USB Configuration & Options |                                                   |

| Advanced Setup Options  CPU Configuration Setup & Options  IDE Configuration Setup & Options  IDE Device Setup Setup & Options  Floppy Configuration Setup & Options  SuperIO Configuration Setup & Options  ACPI Configuration  Advanced ACPI Configuration & Options  Chipset ACPI Configuration and Options  AHCI Configuration  AHCI Port 0  MPS Configuration Setup & Options                              |                                                   |

| Boot Setup                                | 6-1  |

|-------------------------------------------|------|

| Boot Setup & Options                      | 6-1  |

| Boot Settings Configuration & Options     | 6-3  |

| Boot Device Priority & Options            | 6-7  |

| Hard Disk Drives & Options                | 6-9  |

| Removable Drives & Options                | 6-11 |

| CD/DVD Drives & Options                   | 6-13 |

| Chipset Setup.                            | 7-1  |

| Chipset Setup & Options                   |      |

| South Bridge Configuration & Options      |      |

| ESB2 PCI-X Hub Configuration & Options    |      |

| Appendix A - BIOS Messages                |      |

| BIOS Beep Codes.                          |      |

| BIOS Error Messages                       |      |

| Bootblock Initialization Code Checkpoints | A-6  |

| Bootblock Recovery Code Checkpoints.      |      |

| Post Code LEDs                            | A-8  |

| Post Code Checkpoints.                    |      |

| DIM Code Checkpoints                      |      |

| Additional Checkpoints                    | A-12 |

| Appendix B - Power Connection             |      |

| Introduction                              |      |

| Power Supply and SHB Interaction          |      |

| Electrical Connection Configurations      | B-2  |

| ACPI Connection                           | B-2  |

| Legacy Non-ACPI Connection                | B-3  |

| Appendix C - PCI Express™ Backplane Usage |      |

| Introduction                              |      |

| SUR Edge Connectors                       | C 1  |

| Appendix D - I/O Expansion Boards   |     |

|-------------------------------------|-----|

| Introduction                        |     |

| Models                              |     |

| Features                            |     |

| Temperature/Environment             |     |

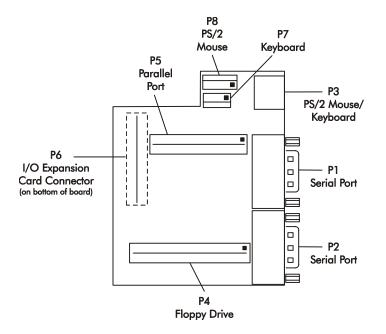

| IOB30MC (6391-001) I/O Board Layout | D-2 |

| IOB30MC Connectors                  |     |

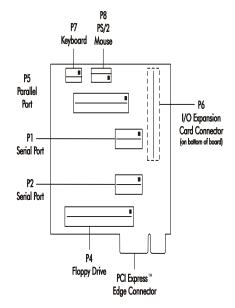

| IOB31 (6474-000) Block Diagram      |     |

| IOB31 (6474-000) I/O Board Layout   |     |

| IOB31 Connectors                    | D-7 |

# HANDLING PRECAUTIONS

**WARNING:** This product has components which may be damaged by electrostatic discharge.

To protect your system host board (SHB) from electrostatic damage, be sure to observe the following precautions when handling or storing the board:

- Keep the SHB in its static-shielded bag until you are ready to perform your installation.

- Handle the SHB by its edges.

- Do not touch the I/O connector pins. Do not apply pressure or attach labels to the SHB.

- Use a grounded wrist strap at your workstation or ground yourself frequently by touching the metal chassis of the system before handling any components. The system must be plugged into an outlet that is connected to an earth ground.

- Use antistatic padding on all work surfaces.

- Avoid static-inducing carpeted areas.

# SOLDER-SIDE COMPONENTS

This SHB has components on both sides of the PCB. It is important for you to observe the following precautions when handling or storing the board to prevent solder-side components from being damaged or broken off:

- Handle the board only by its edges.

- Store the board in padded shipping material or in an anti-static board rack.

- Do not place an unprotected board on a flat surface.

This page intentionally left blank.

### Chapter 1 Specifications

#### INTRODUCTION

The MCX series processor boards are full-featured server-class system host boards (SHBs). The MCXT (506633-xxx) features two dual- or quad-core Intel<sup>®</sup> Xeon<sup>®</sup> microprocessors; the MCXI (506638-xxx) has one dual- or quad-core Intel<sup>®</sup> Xeon<sup>®</sup> microprocessor. Both SHBs provide a 1066MHz or 1333MHz system bus, ATI Technologies<sup>®</sup> video interface, support for 16GB DDR2 memory, PCI Express<sup>™</sup> bus, cache memory, an Ultra ATA/100 drive interface, support for three Gigabit Ethernet interfaces, six Serial ATA ports, support for up to seven USB ports and a speaker port. These single-slot high performance SHBs plug into PICMG<sup>®</sup> 1.3 backplanes and provide full PC compatibility for the system expansion slots.

The MCXT-E (506685-xxx) and MCXI-E (506700-xxx) are extended-memory models which have all of the features of the MCXT/MCXI and support up to 32GB of DDR2 memory.

**NOTE:** In the model number/name tables below, "xG" indicates memory size (0G = 0GB memory, 1G = 1GB memory, etc.)

#### MCXT (506633-XXX) MODELS

#### MCXT Models -- Two Processors, Standard Memory (up to 16GB):

### Model # Model Name Speed

#### **MCXT - Dual-Core Processors:**

Intel<sup>®</sup> Xeon<sup>®</sup> Processors - 1066MHz FSB/4MB cache:

506633-005-xG MCXT/1.86DH 1.86GHz 506633-004-xG MCXT/1.6DH 1.6GHz

Intel<sup>®</sup> Xeon<sup>®</sup> Processors - 1333MHz FSB/4MB cache:

506633-112-xG

MCXT/3.0DK

3.0GHz

506633-110-xG

MCXT/2.66DK

2.66GHz

506633-108-xG

MCXT/2.33DK

2.33GHz

506633-106-xG

MCXT/2.0DK

2.0GHz

$\mathsf{Intel}^{\circledR} \, \mathsf{Xeon}^{\circledR} \, \mathsf{Processors}$  - Low Voltage - 1333MHz FSB/4MB cache:

506633-308-xG MCXT/2.33LK 2.33GHz

Intel<sup>®</sup> Xeon<sup>®</sup> Processors - 1333MHz FSB/6MB cache:

506633-132-xG MCXT/3.0FK 3.0GHz 506633-128-xG MCXT/2.33FK 2.33GHz

Intel<sup>®</sup> Xeon<sup>®</sup> Processors - Low Voltage - 1333MHz FSB/6MB cache:

506633-232-xG MCXT/3.0FLK 3.0GHz 506633-230-xG MCXT/2.66FLK 2.66GHz

Intel<sup>®</sup> Xeon<sup>®</sup> Processors - Extreme - 1333MHz FSB/6MB cache:

506633-363-xG MCXT/3.5FX 3.5GHz 506633-362-xG MCXT/3.33FX 3.33GHz

| Model # Model Name                                                         |                       | <b>Speed</b>             |  |  |  |  |

|----------------------------------------------------------------------------|-----------------------|--------------------------|--|--|--|--|

| MCXT - Quad-Core Processors:                                               |                       |                          |  |  |  |  |

| Intel <sup>®</sup> Xeon <sup>®</sup> Processors - 1066MHz FSB/2x4MB cache: |                       |                          |  |  |  |  |

| 506633-405-xG                                                              |                       |                          |  |  |  |  |

| 506633-404-xG                                                              | MCXT/1.6QH            | 1.6GHz                   |  |  |  |  |

| Intel <sup>®</sup> Xeon <sup>®</sup> Proce                                 | ssors - Low Voltage - | 1066MHz FSB/2x4MB cache: |  |  |  |  |

| 506633-605-xG                                                              | MCXT/1.86QLH          | 1.86GHz                  |  |  |  |  |

| 506633-604-xG                                                              | MCXT/1.6QLH           | 1.6GHz                   |  |  |  |  |

| 506633-603-xG                                                              | MCXT/1.6aQLH          | 1.6GHz (ATCA)            |  |  |  |  |

| Intel <sup>®</sup> Xeon <sup>®</sup> Proce                                 | ssors - Extreme - 106 | 6MHz FSB/2x4MB cache:    |  |  |  |  |

| 506633-573-xG                                                              | MCXT/2.66QX           | 2.66GHz                  |  |  |  |  |

| Intel <sup>®</sup> Xeon <sup>®</sup> Proce                                 | ssors - Low Voltage - | 1333MHz FSB/2x4MB cache: |  |  |  |  |

| 506633-706-xG                                                              | MCXT/2.0QLK           | 2.0GHz                   |  |  |  |  |

| Intel <sup>®</sup> Xeon <sup>®</sup> Proce                                 | ssors - 1333MHz FSI   | B/2x4MB cache:           |  |  |  |  |

| 506633-508-xG                                                              | MCXT/2.33QK           | 2.33GHz                  |  |  |  |  |

| 506633-506-xG                                                              | MCXT/2.0QK            | 2.0GHz                   |  |  |  |  |

| Intel <sup>®</sup> Xeon <sup>®</sup> Proce                                 | ssors - 1333MHz FSI   | B/2x6MB cache:           |  |  |  |  |

| 506633-812-xG                                                              | MCXT/3.0RK            | 3.0GHz                   |  |  |  |  |

| 506633-811-xG                                                              | MCXT/2.83RK           | 2.83GHz                  |  |  |  |  |

| 506633-810-xG                                                              | MCXT/2.66RK           | 2.66GHz                  |  |  |  |  |

| 506633-809-xG                                                              | MCXT/2.5RK            | 2.5GHz                   |  |  |  |  |

| 506633-808-xG                                                              | MCXT/2.33RK           | 2.33GHz                  |  |  |  |  |

| 506633-806-xG                                                              | MCXT/2.0RK            | 2.0GHz                   |  |  |  |  |

| Intel <sup>®</sup> Xeon <sup>®</sup> Proce                                 | ssors - Low Voltage - | 1333MHz FSB/2x6MB cache: |  |  |  |  |

| 506633-910-xG                                                              | MCXT/2.66RLK          | 2.66GHz                  |  |  |  |  |

| 506633-909-xG                                                              | MCXT/2.5RLK           | 2.5GHz                   |  |  |  |  |

| 506633-908-xG                                                              | MCXT/2.33RLK          | 2.33GHz                  |  |  |  |  |

| Intel <sup>®</sup> Xeon <sup>®</sup> Proce                                 | ssors - Extreme - 133 | 3MHz FSB/2x6MB cache:    |  |  |  |  |

| 506633-874-xG                                                              | MCXT/3.33RX           | 3.33GHz                  |  |  |  |  |

| 506633-873-xG                                                              | MCXT/3.16RX           | 3.16GHz                  |  |  |  |  |

| 506633-872-xG                                                              | MCXT/3.0RX            | 3.0GHz                   |  |  |  |  |

#### MCXT-E (506685-XXX) MODELS

#### MCXT-E Models - Two Processors, Extended Memory (up to 32GB):

Model # Model Name Speed

#### **MCXT-E - Dual-Core Processors:**

Intel<sup>®</sup> Xeon<sup>®</sup> Processors - 1066MHz FSB/4MB cache:

506685-005-xG MCXT-E/1.86DH 1.86GHz 506685-004-xG MCXT-E/1.6DH 1.6GHz

Intel<sup>®</sup> Xeon<sup>®</sup> Processors - 1333MHz FSB/4MB cache:

506685-112-xG

MCXT-E/3.0DK

3.0GHz

506685-110-xG

MCXT-E/2.66DK

2.66GHz

506685-108-xG

MCXT-E/2.33DK

2.33GHz

506685-106-xG

MCXT-E/2.0DK

2.0GHz

Intel<sup>®</sup> Xeon<sup>®</sup> Processors - Low Voltage - 1333MHz FSB/4MB cache:

506685-308-xG MCXT-E/2.33LK 2.33GHz

Intel<sup>®</sup> Xeon<sup>®</sup> Processors - 1333MHz FSB/6MB cache:

506685-132-xG MCXT-E/3.0FK 3.0GHz 506685-128-xG MCXT-E/2.33FK 2.33GHz

Intel® Xeon® Processors - Low Voltage - 1333MHz FSB/6MB cache:

506685-232-xG MCXT-E/3.0FLK 3.0GHz 506685-230-xG MCXT-E/2.66FLK 2.66GHz

Intel® Xeon® Processors - Extreme - 1333MHz FSB/6MB cache:

506685-363-xG MCXT-E/3.5FX 3.5GHz 506685-362-xG MCXT-E/3.33FX 3.33GHz

#### **MCXT-E - Ouad-Core Processors:**

Intel<sup>®</sup> Xeon<sup>®</sup> Processors - 1066MHz FSB/2x4MB cache:

506685-405-xG MCXT-E/1.86QH 1.86GHz 506685-404-xG MCXT-E/1.6QH 1.6GHz

Intel<sup>®</sup> Xeon<sup>®</sup> Processors - Low Voltage - 1066MHz FSB/2x4MB cache:

506685-605-xG

MCXT-E/1.86QLH

1.86GHz

506685-604-xG

MCXT-E/1.6QLH

1.6GHz

506685-603-xG MCXT-E/1.6aQLH 1.6GHz (ATCA)

Intel® Xeon® Processors - Extreme - 1066MHz FSB/2x4MB cache:

506685-573-xG MCXT-E/2.66QX 2.66GHz

$Intel ^{\circledR} \ Xeon ^{\circledR} \ Processors - Low \ Voltage - 1333MHz \ FSB/2x4MB \ cache:$

506685-706-xG MCXT-E/2.0QLK 2.0GHz

```

Intel<sup>®</sup> Xeon<sup>®</sup> Processors - 1333MHz FSB/2x4MB cache:

506685-508-xG

MCXT-E/2.33QK

2.33GHz

506685-506-xG

MCXT-E/2.0QK

2.0GHz

Intel<sup>®</sup> Xeon<sup>®</sup> Processors - 1333MHz FSB/2x6MB cache:

506685-812-xG

MCXT-E/3.0RK

3.0GHz

506685-811-xG

MCXT-E/2.83RK

2.83GHz

506685-810-xG

MCXT-E/2.66RK

2.66GHz

506685-809-xG

MCXT-E/2.5RK

2.5GHz

506685-808-xG

MCXT-E/2.33RK

2.33GHz

506685-806-xG

MCXT-E/2.0RK

2.0GHz

Intel^{\circledR}\ Xeon^{\circledR}\ Processors - Low\ Voltage - 1333MHz\ FSB/2x6MB\ cache:

MCXT-E/2.66RLK 2.66GHz

506685-910-xG

506685-909-xG

MCXT-E/2.5RLK

2.5GHz

506685-908-xG

MCXT-E/2.33RLK 2.33GHz

Intel^{\circledR} Xeon^{\circledR} Processors - Extreme - 1333MHz FSB/2x6MB cache:

506685-874-xG

MCXT-E/3.33RX

3.33GHz

506685-873-xG

MCXT-E/3.16RX

3.16GHz

506685-872-xG

MCXT-E/3.0RX

3.0GHz

```

#### MCXI (506638-XXX) MODELS

#### MCXI Models -- One Processor, Standard Memory (up to 16GB):

| Model #                                                                  | Model Name                                                                            | <b>Speed</b> |  |  |  |  |  |

|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--------------|--|--|--|--|--|

| MCXI - Dual-Core Processor:                                              |                                                                                       |              |  |  |  |  |  |

| Intel <sup>®</sup> Xeon <sup>®</sup> Proc                                | essor - 1066MHz FS                                                                    | B/4MB cache: |  |  |  |  |  |

| 506638-045-xG                                                            | MCXI/1.86DH                                                                           | 1.86GHz      |  |  |  |  |  |

| 506638-044-xG                                                            | MCXI/1.6DH                                                                            | 1.6GHz       |  |  |  |  |  |

| Intel <sup>®</sup> Xeon <sup>®</sup> Proc                                | essor - 1333MHz FS                                                                    | B/4MB cache: |  |  |  |  |  |

| 506638-152-xG                                                            | MCXI/3.0DK                                                                            | 3.0GHz       |  |  |  |  |  |

| 506638-150-xG                                                            | MCXI/2.66DK                                                                           | 2.66GHz      |  |  |  |  |  |

| 506638-148-xG                                                            | MCXI/2.33DK                                                                           | 2.33GHz      |  |  |  |  |  |

| 506638-146-xG                                                            | MCXI/2.0DK                                                                            | 2.0GHz       |  |  |  |  |  |

| Intel <sup>®</sup> Xeon <sup>®</sup> Proce                               | Intel <sup>®</sup> Xeon <sup>®</sup> Processor - Low Voltage - 1333MHz FSB/4MB cache: |              |  |  |  |  |  |

| 506638-348-xG                                                            | MCXI/2.33LK                                                                           | 2.33GHz      |  |  |  |  |  |

| Intel <sup>®</sup> Xeon <sup>®</sup> Processors - 1333MHz FSB/6MB cache: |                                                                                       |              |  |  |  |  |  |

| 506638-172-xG                                                            | MCXI/3.0FK                                                                            | 3.0GHz       |  |  |  |  |  |

| 506638-168-xG                                                            | MCXI/2.33FK                                                                           | 2.33GHz      |  |  |  |  |  |

### MCXI (506638-xxx) MODELS (CONTINUED)

### MCXI Models -- One Processor, Standard Memory (up to 16GB) (cont'd):

| Model #                                                                   | Model Name                                                                               | <b>Speed</b>             |  |  |  |  |

|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--------------------------|--|--|--|--|

| Intel <sup>®</sup> Xeon <sup>®</sup> Proces                               | ssors - Low Voltage -                                                                    | 1333MHz FSB/6MB cache:   |  |  |  |  |

| 506638-272-xG                                                             | MCXI/3.0FLK                                                                              | 3.0GHz                   |  |  |  |  |

| 506638-270-xG                                                             | MCXI/2.66FLK                                                                             | 2.66GHz                  |  |  |  |  |

| Intel <sup>®</sup> Xeon <sup>®</sup> Proces                               | ssors - Extreme - 1333                                                                   | 3MHz FSB/6MB cache:      |  |  |  |  |

| 506638-369-xG                                                             | MCXI/3.5FX                                                                               | 3.5GHz                   |  |  |  |  |

| 506638-368-xG                                                             | MCXI/3.33FX                                                                              | 3.33GHz                  |  |  |  |  |

| MCXI - Quad-Cor                                                           | e Processor:                                                                             |                          |  |  |  |  |

| Intel <sup>®</sup> Xeon <sup>®</sup> Proces                               | ssor - 1066MHz FSB/                                                                      | 2x4MB cache:             |  |  |  |  |

| 506638-445-xG                                                             | MCXI/1.86QH                                                                              | 1.86GHz                  |  |  |  |  |

| 506638-444-xG                                                             | MCXI/1.6QH                                                                               | 1.6GHz                   |  |  |  |  |

| Intel <sup>®</sup> Xeon <sup>®</sup> Proces                               | ssors - Low Voltage -                                                                    | 1066MHz FSB/2x4MB cache: |  |  |  |  |

| 506638-645-xG                                                             | MCXI/1.86QLH                                                                             | 1.86GHz                  |  |  |  |  |

| 506638-644-xG                                                             | MCXI/1.6QLH                                                                              | 1.6GHz                   |  |  |  |  |

| 506638-643-xG                                                             | MCXI/1.6aQLH                                                                             | 1.6GHz (ATCA)            |  |  |  |  |

| Intel <sup>®</sup> Xeon <sup>®</sup> Proces                               | ssors - Extreme - 1060                                                                   | 6MHz FSB/2x4MB cache:    |  |  |  |  |

| 506638-578-xG                                                             | MCXI/2.66QX                                                                              | 2.66GHz                  |  |  |  |  |

| Intel <sup>®</sup> Xeon <sup>®</sup> Proces                               | Intel <sup>®</sup> Xeon <sup>®</sup> Processors - Low Voltage - 1333MHz FSB/2x4MB cache: |                          |  |  |  |  |

| 506638-746-xG                                                             | MCXI/2.0QLK                                                                              | 2.0GHz                   |  |  |  |  |

| Intel <sup>®</sup> Xeon <sup>®</sup> Processor - 1333MHz FSB/2x4MB cache: |                                                                                          |                          |  |  |  |  |

|                                                                           | MCXI/2.33QK                                                                              |                          |  |  |  |  |

| 506638-546-xG                                                             | MCXI/2.0QK                                                                               | 2.0GHz                   |  |  |  |  |

| Intel <sup>®</sup> Xeon <sup>®</sup> Proces                               | ssors - 1333MHz FSE                                                                      | 3/2x6MB cache:           |  |  |  |  |

| 506638-852-xG                                                             | MCXI/3.0RK                                                                               | 3.0GHz                   |  |  |  |  |

| 506638-851-xG                                                             | MCXI/2.83RK                                                                              | 2.83GHz                  |  |  |  |  |

| 506638-850-xG                                                             | MCXI/2.66RK                                                                              | 2.66GHz                  |  |  |  |  |

| 506638-849-xG                                                             | MCXI/2.5RK                                                                               | 2.5GHz                   |  |  |  |  |

| 506638-848-xG                                                             | MCXI/2.33RK                                                                              | 2.33GHz                  |  |  |  |  |

| 506638-846-xG                                                             | MCXI/2.0RK                                                                               | 2.0GHz                   |  |  |  |  |

| Intel <sup>®</sup> Xeon <sup>®</sup> Proces                               | ssors - Low Voltage -                                                                    | 1333MHz FSB/2x6MB cache: |  |  |  |  |

| 506638-950-xG                                                             | MCXI/2.66RLK                                                                             | 2.66GHz                  |  |  |  |  |

| 506638-949-xG                                                             | MCXI/2.5RLK                                                                              | 2.5GHz                   |  |  |  |  |

| 506638-948-xG                                                             | MCXI/2.33RLK                                                                             | 2.33GHz                  |  |  |  |  |

| Model #                                     | Model Name            | <b>Speed</b>         |

|---------------------------------------------|-----------------------|----------------------|

| Intel <sup>®</sup> Xeon <sup>®</sup> Proces | sors - Extreme - 1333 | MHz FSB/2x6MB cache: |

| 506638-879-xG                               | MCXI/3.33RX           | 3.33GHz              |

| 506638-878-xG                               | MCXI/3.16RX           | 3.16GHz              |

| 506638-877-xG                               | MCXI/3.0RX            | 3.0GHz               |

#### MCXI-E (506700-xxx) Models

#### MCXI-E Models - One Processor, Extended Memory (up to 32GB):

| Model # | <b>Model Name</b> | <b>Speed</b> |

|---------|-------------------|--------------|

|---------|-------------------|--------------|

#### **MCXI-E - Dual-Core Processor:**

Intel<sup>®</sup> Xeon<sup>®</sup> Processor - 1066MHz FSB/4MB cache: MCXI-E/1.86DH 506700-045-xG 1.86GHz 506700-044-xG MCXI-E/1.6DH 1.6GHz Intel<sup>®</sup> Xeon<sup>®</sup> Processor - 1333MHz FSB/4MB cache: 506700-152-xG MCXI-E/3.0DK 3.0GHz 506700-150-xG MCXI-E/2.66DK 2.66GHz 506700-148-xG MCXI-E/2.33DK 2.33GHz 506700-146-xG MCXI-E/2.0DK 2.0GHz Intel<sup>®</sup> Xeon<sup>®</sup> Processor - Low Voltage - 1333MHz FSB/4MB cache: 506700-348-xG MCXI-E/2.33LK 2.33GHz Intel<sup>®</sup> Xeon<sup>®</sup> Processors - 1333MHz FSB/6MB cache: MCXI-E/3.0FK 506700-172-xG 3.0GHz 506700-168-xG MCXI-E/2.33FK 2.33GHz Intel<sup>®</sup> Xeon<sup>®</sup> Processors - Low Voltage - 1333MHz FSB/6MB cache: 506700-272-xG MCXI-E/3.0FLK 3.0GHz 506700-270-xG MCXI-E/2.66FLK 2.66GHz Intel<sup>®</sup> Xeon<sup>®</sup> Processors - Extreme - 1333MHz FSB/6MB cache: 506700-369-xG MCXI-E/3.5FX 3.5GHz 506700-368-xG MCXI-E/3.33FX 3.33GHz

#### **MCXI-E - Quad-Core Processor:**

```

Intel<sup>®</sup> Xeon<sup>®</sup> Processor - 1066MHz FSB/2x4MB cache:

```

506700-445-xG MCXI-E/1.86QH 1.86GHz 506700-444-xG MCXI-E/1.6QH 1.6GHz

Intel<sup>®</sup> Xeon<sup>®</sup> Processors - Low Voltage - 1066MHz FSB/2x4MB cache:

506700-645-xG MCXI-E/1.86QLH 1.86GHz 506700-644-xG MCXI-E/1.6QLH 1.6GHz

506700-643-xG MCXI-E/1.6aQLH 1.6GHz (ATCA)

Intel<sup>®</sup> Xeon<sup>®</sup> Processors - Extreme - 1066MHz FSB/2x4MB cache:

506700-578-xG MCXI-E/2.66QX 2.66GHz

Intel<sup>®</sup> Xeon<sup>®</sup> Processors - Low Voltage - 1333MHz FSB/2x4MB cache:

506700-746-xG MCXI-E/2.0QLK 2.0GHz

Intel<sup>®</sup> Xeon<sup>®</sup> Processor - 1333MHz FSB/2x4MB cache:

506700-548-xG MCXI-E/2.33QK 2.33GHz 506700-546-xG MCXI-E/2.0QK 2.0GHz

Intel<sup>®</sup> Xeon<sup>®</sup> Processors - 1333MHz FSB/2x6MB cache:

506700-852-xG

MCXI-E/3.0RK

3.0GHz

506700-851-xG

MCXI-E/2.83RK

2.83GHz

506700-850-xG

MCXI-E/2.66RK

2.66GHz

506700-849-xG MCXI-E/2.5RK 2.5GHz 506700-848-xG MCXI-E/2.33RK 2.33GHz

506638-846-xG MCXI-E/2.0RK 2.0GHz

$Intel^{\circledR}\ Xeon^{\circledR}\ Processors - Low\ Voltage - 1333MHz\ FSB/2x6MB\ cache:$

506700-950-xG MCXI-E/2.66RLK 2.66GHz 506700-949-xG MCXI-E/2.5RLK 2.5GHz 506700-948-xG MCXI-E/2.33RLK 2.33GHz

$Intel^{\circledR}$  Xeon $^{\circledR}$  Processors - Extreme - 1333MHz FSB/2x6MB cache:

506700-879-xG MCXI-E/3.33RX 3.33GHz 506700-878-xG MCXI-E/3.16RX 3.16GHz 506700-877-xG MCXI-E/3.0RX 3.0GHz

#### **FEATURES**

- Two Intel<sup>®</sup> Xeon<sup>®</sup> microprocessors (MCXT/MCXT-E) or one Intel<sup>®</sup> Xeon<sup>®</sup> microprocessor (MCXI/MCXI-E)

- Dual-core or quad-core processors

# FEATURES (CONTINUED)

- MCXT and MCXI models support up to 16GB of Double Data Rate (DDR2) onboard memory; extended-memory MCXT-E and MCXI-E models support up to 32GB of DDR2 memory

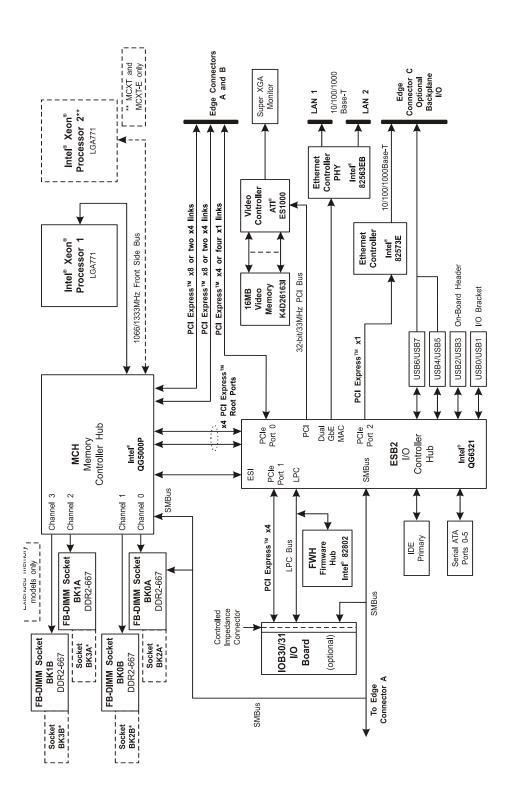

- Intel<sup>®</sup> 5000P chipset with 1066/1333MHz system bus

- PCI Local Bus operating in 32-bit/33MHz mode and PCI Express<sup>™</sup> Bus operating in x4 and x8 modes

- Super XGA on-board video interface (ATI Technologies®)

- Supports three Ethernet interfaces for use with 10/100/1000Base-T networks

- Six Serial ATA ports support independent SATA I and SATA II storage devices

- Memory error checking and correction (ECC) support

- Compatible with PCI Industrial Computer Manufacturers Group (PICMG®) 1.3 Specification

- Ultra ATA/100 drive interface supports two drives in a master/slave configuration

- Universal Serial Bus (USB 2.0) support

- Automatic or manual peripheral configuration

- Full PC compatibility

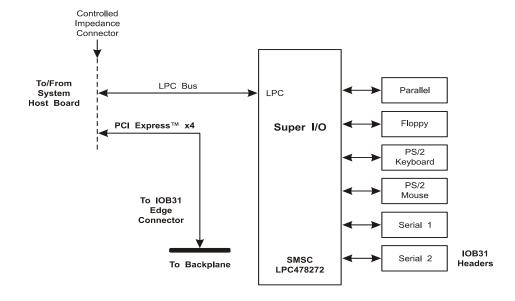

#### MCX SERIES SHB BLOCK DIAGRAM

MCXT (506633-XXX) SHB BOARD LAYOUT

MCXT-E (506685-XXX) SHB BOARD LAYOUT

MCXI (506638-XXX) SHB BOARD LAYOUT

MCXI-E (506700-XXX) SHB BOARD LAYOUT

#### **PROCESSORS**

- Two Intel<sup>®</sup> Xeon<sup>®</sup> microprocessors (MCXT/MCXT-E) or one Intel<sup>®</sup> Xeon<sup>®</sup> microprocessor (MCXI/MCXI-E)

- Dual-core or quad-core processors

- Processors use the LGA771 (Socket J) packaging

**BUS INTERFACES**

PCI Local Bus compatible

**DATA PATH**

DDR2 Memory - 64-bit (per channel)

PCI Bus - 32-bit

**BUS SPEEDS**

PCI - 33MHz (on-board only)

PCI Express - 2.5GHz per lane

BUS SPEED -SYSTEM 1066MHz or 1333MHz Front Side Bus

MEMORY INTERFACE The SHB uses Double Data Rate (DDR2) memory. Theoretical memory interface bandwidth is a maximum of 8.0GB/s when using PC2-5300 DIMMs

SYSTEM BUS

Intel<sup>®</sup> 5000P chipset supports the system bus at 1066MHz or 1333MHz, which provides a higher bandwidth path for transferring data between main memory/chipset and the processors.

**DMA CHANNELS**

The SHB is fully PC compatible with seven DMA channels, each supporting type F transfers.

**INTERRUPTS**

The SHB is fully PC compatible with interrupt steering for PCI plug and play compatibility.

**BIOS (FLASH)**

The BIOS is an AMIBIOS with built-in advanced CMOS setup for system parameters, peripheral management for configuring on-board peripherals and other system parameters. The Flash BIOS resides in the Intel<sup>®</sup> 82802AC Firmware Hub (FWH). The BIOS may be upgraded from floppy disk by pressing **<Ctrl>** + **<Home>** immediately after reset or power-up with the floppy disk in drive A:. Custom BIOSs are available.

**CACHE MEMORY**

The processors include integrated on-die, 8-way set associative level two (L2) cache, which implements the Advanced Transfer Cache architecture and runs at the full speed of the processor core. The dual-core Intel<sup>®</sup> Xeon<sup>®</sup> processors have 4M of shared L2 cache memory; the quad-core processors have 2 x 4M of L2 cache memory. Both types of processors have 32K level 1 (L1) instruction cache and 32K L1 data cache per core.

#### **DDR2 MEMORY**

The Double Data Rate (DDR2) memory interface on the MCXT and MCXI SHBs supports up to 16GB of memory; the MCXT-E and MCXI-E models support up to 32GB of memory.

The SHB uses industry standard 72-bit wide ECC gold finger memory modules in four (MCXT/MCXI) or eight (MCXT-E/MCXI-E) 240-pin sockets. The FB-DIMMs must be PC2-4200 or PC2-5300 (DDR2-533 or DDR2-667) and comply with the JEDEC Rev. 2.0 specifications.

FB-DIMMs have "Advanced Memory Buffer" chips that provide enhanced signal integrity and improved error detection that help reduce soft memory errors. FB-DIMM memory technology improves overall system reliability by extending the current ECC capability to include protection of command and address data. FB-DIMMs feature automatic retries when a memory error is detected, which results in uninterrupted system operation in the event of transient errors.

The following FB-DIMM sizes are supported:

| DIMM<br>Size | DIMM Type  | <u>ECC</u> |

|--------------|------------|------------|

| 512MB        | Registered | 64M x 72   |

| 1GB          | Registered | 128M x 72  |

| 2GB          | Registered | 256M x 72  |

| 4GB          | Registered | 512M x 72  |

|              |            |            |

**NOTE:** With the bracket end of the board to the right, the four FB-DIMM sockets available on the MCXT and MCXI SHBs are numbered BK0A, BK1A, BK0B and BK1B, from top to bottom. On the extended-memory MCXT-E and MCXI-E SHBs, there are an additional four FB-DIMM sockets. The upper sockets are BK2A and BK2B, from left to right, and the lower sockets are BK3A and BK3B. These socket definitions are illustrated in the board layouts earlier in this chapter. All memory modules must have gold contacts.

A minimum of one 512MB FB-DIMM is required and must be populated in DIMM socket BK0A. When using more than one FB-DIMM, the memory sockets must be populated in multiples of two in order to maximize the speed and performance of the memory interface.

To take full advantage of the four-channel memory interface of the SHB's memory controller hub, the FB-DIMMs in sockets BK0A and BK1A must be identical in manufacturing, speed, timing and organization. FB-DIMMs in sockets BK0B and BK1B must also be identical. FB-DIMMs in sockets contained within the same memory channel (e.g., BK0A and BK2A) do not have to be identical.

|                                    | FB-DIMM Sockets (All Models)         |                                       |                                        | FB-DIMM Sockets (MCXT-E/MCXI-E)        |                                         |                                         |                                          |                                          |

|------------------------------------|--------------------------------------|---------------------------------------|----------------------------------------|----------------------------------------|-----------------------------------------|-----------------------------------------|------------------------------------------|------------------------------------------|

| Number of<br>FB-DIMM<br>Modules    | <u>BK0A</u> *                        | BK1A                                  | BK0B                                   | <u>BK1B</u>                            | BK2A                                    | BK2B                                    | BK3A                                     | BK3B                                     |

| One<br>Two<br>Four<br>Six<br>Eight | DIMM<br>DIMM<br>DIMM<br>DIMM<br>DIMM | Empty<br>DIMM<br>DIMM<br>DIMM<br>DIMM | Empty<br>Empty<br>DIMM<br>DIMM<br>DIMM | Empty<br>Empty<br>DIMM<br>DIMM<br>DIMM | Empty<br>Empty<br>Empty<br>DIMM<br>DIMM | Empty<br>Empty<br>Empty<br>DIMM<br>DIMM | Empty<br>Empty<br>Empty<br>Empty<br>DIMM | Empty<br>Empty<br>Empty<br>Empty<br>DIMM |

The following table illustrates the FB-DIMM population rules:

# ERROR CHECKING AND CORRECTION

The memory interface supports ECC modes via BIOS setting for multiple-bit error detection and correction of all errors confined to a single nibble.

#### **BUS INTERFACES**

The PCI Local Bus, which is 32 bits wide and runs at 33MHz, interfaces to the ATI Technologies ES1000 video controller.

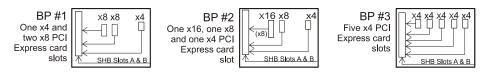

The SHB provides two x8 PCI Express links, one x4 PCI Express link and eight PCI Express reference clocks on Edge Connectors A and B. Each of the x8 links can be bifurcated into two x4 PCIe links; the single x4 PCIe link can be divided into four x1 PCIe links. The SHB also provides a x4 link to the controlled impedance connector for use with PCI Express plug-in option cards. Refer to the *PCI Express Reference* chapter of this manual for more information, including edge connector pin assignments.

#### UNIVERSAL SERIAL BUS (USB)

The SHB supports up to eight high-speed USB 2.0 ports. Connectors for two of the USB ports (0 and 1) are on the I/O bracket; two ports (2 and 3) are available via a header on the SHB. USB ports 4, 5, 6 and 7 are routed to edge connector C of the SHB for use on a PICMG 1.3 backplane which supports the optional PICMG 1.3 USB interface capability.

#### SUPER XGA INTERFACE

The ATI Technologies ES1000 video controller provides 16MB of on-board video memory via an external memory chip. The video controller supports pixel resolutions up to 1280 x 1024 (SXGA).

Software drivers are available for most popular operating systems.

### ETHERNET INTERFACES

The SHB provides three Ethernet interfaces, each supporting up to 1Gb/s transfers.

Two of the Ethernet interfaces are implemented using an Intel<sup>®</sup> 82563EB Ethernet controller with two channels. These interfaces support Gigabit, 10Base-T and 100Base-TX Fast Ethernet modes and are compliant with the IEEE 802.3 Specification.

The Intel<sup>®</sup> 82563EB Ethernet controller provides:

• Integrated RJ-45/Magnetics module connectors on the SHB's I/O bracket for direct connection to the network. The connectors require category 5 (CAT5) unshielded twisted-pair (UTP) 2-pair cables for a 100-Mb/s network connection or category3 (CAT3) or higher UTP 2-pair cables for a 10-Mb/s network connection. Category 5e (CAT5e) or higher UTP 2-pair cables are recommended for a 1000-Mb/s (Gigabit) network connection.

<sup>\*</sup> BK0A is the top-most DIMM on the MCXT and MCXI models.

• Link status and activity LEDs on the I/O bracket for status indication (See *Ethernet LEDs and Connectors* later in this chapter.)

The third LAN is supported by the ESB2 I/O controller hub via a x1 PCI Express bus to an Intel<sup>®</sup> 82573E Ethernet controller. This 10/100/1000Base-T Ethernet interface is routed to the PICMG 1.3 backplane via edge connector C of the SHB.

Software drivers are supplied for most popular operating systems.

#### SERIAL ATA/300 PORTS

The six Serial ATA (SATA) ports on the SHB comply with the SATA specification and support six independent SATA I or SATA II storage devices such as hard disks and CD-RW devices. SATA produces higher performance interfacing by providing data transfer rates up to 300MB per second on each port. The SHB supports RAID 0, 1, 5 and 10 array configurations.

# ENHANCED IDE INTERFACE

The high performance PCI Bus Master EIDE interface is capable of supporting two IDE disk drives in a master/slave configuration. The interface supports Ultra ATA/100 with synchronous ATA mode transfers up to 100MB per second. Ultra ATA/100 cables must be used with Ultra ATA/100 drives.

#### **BATTERY**

A built-in lithium battery is provided, for ten years of data retention for CMOS memory.

**CAUTION:** There is a danger of explosion if the battery is incorrectly replaced. Replace it only with the same or equivalent type recommended by the manufacturer. Dispose of used batteries according to the manufacturer's instructions.

# POWER REQUIREMENTS

The following are typical values \*:

2.33GHz (LV) 2.00 Amps

Processor

| Speed                                         | <u>+5V</u> | <u>+12V</u> | <u>+3.3V</u> | <u>-12V</u> |  |

|-----------------------------------------------|------------|-------------|--------------|-------------|--|

| 100% CPU Idle State - 4GB of system memory:   |            |             |              |             |  |

| 2.0GHz **                                     | 1.75 Amps  | 7.50 Amps   | 3.00 Amps    | < 100 mAmps |  |

| 2.33GHz                                       | 1.75 Amps  | 5.90 Amps   | 3.00 Amps    | < 100 mAmps |  |

| 2.0GHz                                        | 1.75 Amps  | 5.80 Amps   | 3.00 Amps    | < 100 mAmps |  |

| 2.33GHz (LV)                                  | 1.75 Amps  | 5.70 Amps   | 3.00 Amps    | < 100 mAmps |  |

| 100% CPU Stress State - 4GB of system memory: |            |             |              |             |  |

| 2.0GHz **                                     | 2.00 Amps  | 15.60 Amps  | 3.20 Amps    | < 100 mAmps |  |

| 2.33GHz                                       | 2.00 Amps  | 12.80 Amps  | 3.20 Amps    | < 100 mAmps |  |

| 2.0GHz                                        | 2.00 Amps  | 12.70 Amps  | 3.20 Amps    | < 100 mAmps |  |

12.50 Amps 3.20 Amps

< 100 mAmps

- \* Values stated are when using the MCXT-E extended-memory SHB with dual processors.

- \*\* Quad-core processors

Tolerance for all voltages is +/- 5% and must be applied by the PICMG 1.3 backplane to edge connector C.

Each 1GB of additional FB-DIMM system memory will typically draw an additional 0.5A of  $\pm 12V$ .

#### **POWER SUPPLY**

The MCX-series SHB requires a power supply with a minimum of 450 watts. If the power supply does not provide a minimum of 2.0 Amps of 5-volt standby current, the system may not boot.

The default system shutdown option is set to **Manual Shutdown**. This prompts a shutdown screen after the operating system shuts down, which requires a manual power off in A/C power. To automatically shut down the SHB after operating system shutdown, change **Manual Shutdown** to **Auto**. This puts the SHB in S5 power-off state and does not require that a manual power off be done in order to keep the SHB off.

A/C power should always be powered off when any parts are being removed from or connected to the SHB or backplane. Failure to do so may result in serious damage to the SHB or backplane.

#### TEMPERATURE/ ENVIRONMENT

**Operating Temperature:** 0° C. to 55° C. (2.33GHz LV processors)

0° C. to 45° C. (all other processors)

**Airflow Requirement:** 300 LFM continuous airflow when using the SHB's

standard heat sink

**Storage Temperature:** - 40° C. to 70° C.

**Humidity:** 5% to 90% non-condensing

#### **UL RECOGNITION**

This SHB is a UL recognized product listed in file #E208896.

This board was investigated and determined to be in compliance under the Bi-National Standard for Information Technology Equipment. This included the Electrical Business Equipment, UL 1950, Third Edition, and CAN/CSA C22.22 No. 950-95.

#### MEAN TIME BETWEEN FAILURE (MTBF)

186,261 POH (Power-On Hours) at 40° C., per Bellcore.

# CONFIGURATION JUMPERS

The setup of the configuration jumpers on the SHB is described below. \* indicates the default value of each jumper.

**NOTE:** For two-position jumpers (3-post), "RIGHT" is toward the bracket end of the board; "LEFT" is toward the processor(s).

<u>Jumper</u> <u>Description</u>

JU8 Password Clear

Install for one power-up cycle to reset the password to the default (null password).

Remove for normal operation. \*

#### JU10/JU11 System Flash ROM Operational Modes

The Flash ROM has two programmable sections: the Boot Block for "flashing" in the BIOS and the Main Block for the executable BIOS and PnP parameters. Normally only the Main Block is updated when a new BIOS is flashed into the system.

All Blocks Write Enabled Remove \* Remove \* Boot Block Write Protected Install Remove Block 2-16 Write Protected Remove Install

### JU12 CMOS Clear

Install on the LEFT to clear.

Install on the RIGHT to operate. \*

**NOTE:** To clear the CMOS, power down the system and install the jumper on the LEFT. Wait for at least two seconds, move the jumper back to the RIGHT and turn the power on. When AMIBIOS displays the "CMOS Settings Wrong" message, press F1 to go into the BIOS Setup Utility, where you may reenter your desired BIOS settings, load optimal defaults or load failsafe defaults.

#### JU13 AT Power Supply Operation

Install when using an AT-style system power supply. Remove for all other system power supplies.\*

# ETHERNET LEDS AND CONNECTORS

Each of the two Ethernet interfaces on the SHB's I/O bracket has two LEDs for status indication and an RJ-45 network connector.

| LED/Connector              | <u>Description</u>                                                                                                                                                                                                                                                                                                                      |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Activity LED               | Green LED which indicates network activity. This is the upper LED on the LAN connector (i.e., toward the memory sockets).                                                                                                                                                                                                               |

| Off                        | Indicates that there is no valid link.                                                                                                                                                                                                                                                                                                  |

| On (solid)                 | Indicates a valid link, but no current network transmit or receive activity.                                                                                                                                                                                                                                                            |

| On (flashing)              | Indicates a valid link with network transmit or receive activity.                                                                                                                                                                                                                                                                       |

| Speed LED                  | Green LED which identifies the connection speed. This is the lower LED on the LAN connector (i.e., toward the edge connectors).                                                                                                                                                                                                         |

| Off                        | Indicates a valid link at 100-Mb/s or 10-Mb/s.                                                                                                                                                                                                                                                                                          |

| On (solid)                 | Indicates a valid link at 1000-Mb/s.                                                                                                                                                                                                                                                                                                    |

| RJ-45 Network<br>Connector | The RJ-45 network connector requires a category 5 (CAT5) unshielded twisted-pair (UTP) 2-pair cable for a 100-Mb/s network connection or a category 3 (CAT3) or higher UTP 2-pair cable for a 10-Mb/s network connection. A category 5e (CAT5e) or higher UTP 2-pair cable is recommended for a 1000-Mb/s (Gigabit) network connection. |

#### **LAN3 Link Status LED**

The LAN3 link status LED (LED9), which is located to the right of the Intel 82573E Ethernet controller, indicates the link status of the 10/100/1000Base-T Ethernet connection which is routed to the PICMG 1.3 backplane via edge connector C of the SHB. Status can be determined as shown below:

| LED Status    | <u>Description</u>                                                           |

|---------------|------------------------------------------------------------------------------|

| Off           | Indicates that there is no valid link.                                       |

| On (solid)    | Indicates a valid link, but no current network transmit or receive activity. |

| On (flashing) | Indicates a valid link with network transmit or receive activity.            |

#### STATUS LEDS

#### POST Code LEDs

As the POST (Power On Self Test) routines are performed during boot-up, test codes are displayed on Port 80 POST code LEDs 0 through 7, which are located below the memory banks and are numbered from right (0) to left (7). Refer to the board layouts earlier in this chapter for the exact location of the POST code LEDs.

These POST codes may be helpful as a diagnostic tool. Specific error codes are listed in *Appendix A - BIOS Messages*, along with a chart to interpret the LEDs into hexadecimal format.

### **CPU Throttling LED**

The CPU throttling LED (LED8), which is located in the lower left corner of the SHB to the right of CPU Fan 1 (P19), indicates the status of CPU thermal shutdown, as shown below:

| LED Status    | Description                                                                                                                            |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Off           | Indicates the CPU is operating within acceptable thermal levels.                                                                       |

| On (flashing) | Indicates the CPU is throttling down to a lower operating speed due to rising CPU temperature.                                         |

| On (solid)    | Indicates the CPU has reached the thermal shutdown threshold limit. The SHB is still operating, but a thermal shutdown may soon occur. |

**NOTE:** When a thermal shutdown occurs, the LED will stay on in systems using non-ATX/EPS power supplies. The CPU will cease functioning, but power will still be applied to the SHB. In systems with ATX/EPS power supplies, the LED will turn off when a thermal shutdown occurs because system power is removed via the ACPI soft control power signal S5. In this case, all SHB LEDs will turn off; however, stand-by power will still be present.

#### SYSTEM BIOS SETUP UTILITY

The System BIOS is an AMIBIOS with a ROM-resident setup utility. The BIOS Setup Utility allows you to select to the following categories of options:

- Main Menu

- Advanced Setup

- PCIPnP Setup

- Boot Setup

- Security Setup

- · Chipset Setup

- Exit

Each of these options allows you to review and/or change various setup features of your system. Details are provided in the following chapters of this manual.

#### **CONNECTORS**