# MX8

# 6240-xxx

No. 87-006243-000 Revision A

# **TECHNICAL REFERENCE**

Intel<sup>®</sup> Pentium<sup>®</sup> 4

or

Intel<sup>®</sup> Celeron<sup>®</sup>

PROCESSOR-BASED

SBC

#### WARRANTY

The product is warranted against material and manufacturing defects for two years from date of delivery. Buyer agrees that if this product proves defective Trenton Technology Inc. is only obligated to repair, replace or refund the purchase price of this product at Trenton Technology's discretion. The warranty is void if the product has been subjected to alteration, neglect, misuse or abuse; if any repairs have been attempted by anyone other than Trenton Technology Inc.; or if failure is caused by accident, acts of God, or other causes beyond the control of Trenton Technology Inc. Trenton Technology Inc. reserves the right to make changes or improvements in any product without incurring any obligation to similarly alter products previously purchased.

In no event shall Trenton Technology Inc. be liable for any defect in hardware or software or loss or inadequacy of data of any kind, or for any direct, indirect, incidental or consequential damages arising out of or in connection with the performance or use of the product or information provided. Trenton Technology Inc.'s liability shall in no event exceed the purchase price of the product purchased hereunder. The foregoing limitation of liability shall be equally applicable to any service provided by Trenton Technology Inc.

#### **RETURN POLICY**

Products returned for repair must be accompanied by a Return Material Authorization (RMA) number, obtained from Trenton Technology prior to return. Freight on all returned items must be prepaid by the customer, and the customer is responsible for any loss or damage caused by common carrier in transit. Items will be returned from Trenton Technology via Ground, unless prior arrangements are made by the customer for an alternative shipping method

To obtain an RMA number, call us at (800) 875-6031 or (770) 287-3100. We will need the following information:

Return company address and contact Model name and model # from the label on the back of the board Serial number from the label on the back of the board Description of the failure

An RMA number will be issued. Mark the RMA number clearly on the outside of each box, include a failure report for each board and return the product(s) to our Utica, NY facility:

TRENTON Technology Inc. 1001 Broad Street Utica, NY 13501 Attn: Repair Department

#### **TRADEMARKS**

IBM, PC, VGA, EGA, OS/2 and PS/2 are trademarks or registered trademarks of International Business Machines Corp.

AMI and AMIBIOS are trademarks of American Megatrends Inc.

Intel, Pentium and Celeron are registered trademarks of Intel Corporation.

ATI is a registered trademark of ATI Technologies Incorporated.

MS-DOS and Microsoft are registered trademarks of Microsoft Corp. PICMG and the PICMG logo are registered trademarks of the PCI

Industrial Computer Manufacturers Group.

SCSISelect is a trademark of Adaptec, Inc.

All other brand and product names may be trademarks or registered trademarks of their respective companies.

# LIABILITY DISCLAIMER

This manual is as complete and factual as possible at the time of printing; however, the information in this manual may have been updated since that time. Trenton Technology Inc. reserves the right to change the functions, features or specifications of their products at any time, without notice.

Copyright © 2004 by Trenton Technology Inc. All rights reserved.

E-mail: Support@TrentonTechnology.com Web: www.TrentonTechnology.com

# Table of Contents

| Specifications                     |

|------------------------------------|

| Introduction                       |

| Models                             |

| Features1-2                        |

| SBC Block Diagram1-4               |

| SBC Board Layout                   |

| Processor1-6                       |

| Bus Interfaces                     |

| Data Path                          |

| Bus Speed - PCI and PCI-X          |

| Bus Speed - System                 |

| Memory Interface                   |

| System Bus                         |

| DMA Channels                       |

| Interrupts                         |

| BIOS (Flash)                       |

| Cache Memory                       |

| NetBurst Micro-Architecture        |

| DDR Memory1-7                      |

| Error Checking and Correction      |

| ISA Bus Interface                  |

| PCI-X/PCI Local Bus Interfaces     |

| Universal Serial Bus (USB)         |

| Ultra XGA Interface                |

| System Hardware Monitor            |

| PCI Ethernet Interfaces (Dual)1-9  |

| Hub Interface1-10                  |

| PCI SCSI Interface                 |

| Serial ATA/150 Ports (Dual)        |

| PCI Enhanced IDE Interfaces (Dual) |

| Floppy Drive Interface             |

| Serial Interface                   |

| Enhanced Parallel Interface        |

| PS/2 Mouse Interface               |

| Keyboard Interface                 |

| Watchdog Timer 1-11                |

# Table of Contents

| Specifications (continued)            |      |

|---------------------------------------|------|

| Power Fail Detection                  | 1-11 |

| Battery                               | 1-11 |

| Power Requirements                    | 1-12 |

| Temperature/Environment               | 1-12 |

| Configuration Jumpers                 | 1-13 |

| Ethernet LEDs and Connectors          | 1-14 |

| System BIOS Setup Utility             | 1-15 |

| Connectors                            | 1-16 |

| ISA/PCI Reference                     | 2.1  |

| ISA Bus Pin Numbering.                |      |

| ISA Bus Pin Assignments               |      |

| ISA Bus Signal Descriptions           |      |

|                                       |      |

| I/O Address Map                       |      |

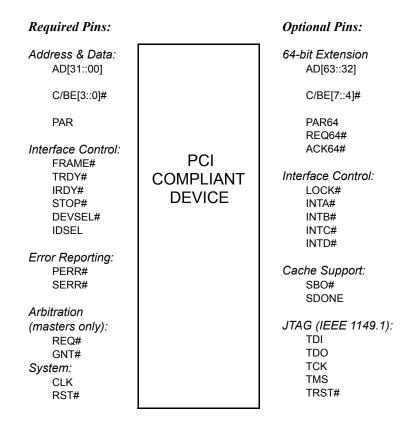

| PCI Local Bus Overview                |      |

| PCI Local Bus Signal Definition       |      |

| PCI Local Bus Pin Numbering           |      |

| PCI Local Bus Pin Assignments         |      |

| PCI Local Bus Signal Descriptions     |      |

| PICMG Edge Connector Pin Assignments  |      |

| FICING Edge Connector Fin Assignments |      |

| System BIOS                           | 3-1  |

| BIOS Operation                        | 3-1  |

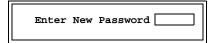

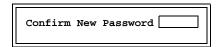

| Password Entry                        | 3-2  |

| BIOS Errors                           | 3-4  |

| Running AMIBIOS Setup                 | 3-5  |

| BIOS Setup Utility Main Menu          | 3-6  |

| BIOS Setup Utility Options            | 3-7  |

| Security Setup                        | 3-11 |

| Change Supervisor Password            | 3-11 |

| Disabling Supervisor Password         | 3-14 |

| Change User Password                  | 3-14 |

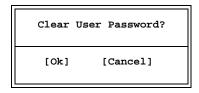

| Clear User Password                   |      |

| Boot Sector Virus Protection          |      |

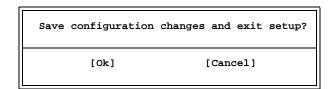

| Evit Menu                             | 3_17 |

# Table of Contents

| Advanced Setup                            | 4-1  |

|-------------------------------------------|------|

| CPU Configuration                         | 4-5  |

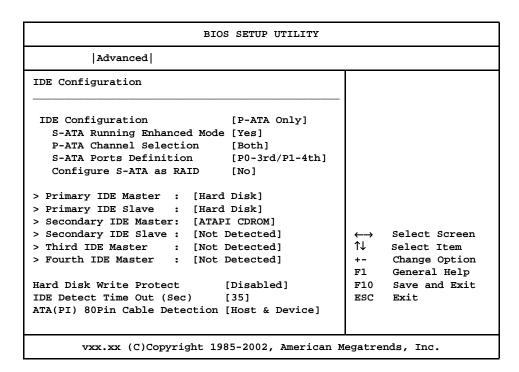

| IDE Configuration                         | 4-7  |

| IDE Device Setup                          | 4-13 |

| Floppy Configuration                      | 4-17 |

| SuperIO Configuration                     | 4-19 |

| Remote Access Configuration               | 4-23 |

| USB Configuration                         | 4-25 |

| PCI Plug and Play Setup                   | 5-1  |

| Boot Setup                                | 6-1  |

| Boot Settings Configuration               | 6-3  |

| Boot Device Priority                      | 6-7  |

| Hard Disk Drives                          | 6-9  |

| Removable Drives                          | 6-11 |

| CD/DVD Drives                             | 6-13 |

| Chipset Setup                             | 7-1  |

| NorthBridge Configuration                 | 7-3  |

| SouthBridge Configuration                 | 7-9  |

| Appendix A - BIOS Messages                | A-1  |

| BIOS Beep Codes                           | A-1  |

| BIOS Error Messages                       | A-2  |

| Bootblock Initialization Code Checkpoints | A-6  |

| Bootblock Recovery Code Checkpoints.      | A-7  |

| Post Code Checkpoints                     | A-8  |

| DIM Code Checkpoints                      | A-10 |

| Additional Checknoints                    | Δ_11 |

This page intentionally left blank.

# HANDLING PRECAUTIONS

**WARNING:** This product has components which may be damaged by electrostatic discharge.

To protect your single board computer (SBC) from electrostatic damage, be sure to observe the following precautions when handling or storing the board:

- Keep the SBC in its static-shielded bag until you are ready to perform your installation.

- Handle the SBC by its edges.

- Do not touch the I/O connector pins. Do not apply pressure or attach labels to the SBC.

- Use a grounded wrist strap at your workstation or ground yourself frequently by touching the metal chassis of the system before handling any components. The system must be plugged into an outlet that is connected to an earth ground.

- Use antistatic padding on all work surfaces.

- Avoid static-inducing carpeted areas.

# SOLDER-SIDE COMPONENTS

This SBC has components on both sides of the PCB. It is important for you to observe the following precautions when handling or storing the board to prevent solder-side components from being damaged or broken off:

- Handle the board only by its edges.

- Store the board in padded shipping material or in an anti-static board rack.

- Do not place an unprotected board on a flat surface.

This page intentionally left blank.

# Before You Begin

#### INTRODUCTION

It is important to be aware of the system considerations listed below before installing your MX8 SBC. Overall system performance may be affected by incorrect usage of these features.

# Mouse/Keyboard "Y" Cable

When using a "Y" cable attached to the bracket mounted mouse/keyboard mini Din connector, be sure to use Trenton's "Y" cable, part number 5886-000. Using a non-Trenton cable may result in improper SBC operation.

#### **DDR Memory**

The memory modules used in the MX8 may be PC2100, PC2700 or PC3200 ECC or non-ECC, unbuffered DIMMs. If two modules of different speeds are used, the DIMMs will operate in dual-channel mode at the speed of the slowest DIMM. If the modules are different sizes, they will operate in single-channel mode. Registered DIMMs are *not* supported. All memory modules must have gold contacts.

In addition, the DIMMs must have the following features:

- 184-pin with gold-plated contacts

- ECC (72-bit) or non-ECC (64-bit) DDR memory

- Unbuffered configuration

#### **BOOT FROM LAN**

The MX8 supports bootup from a LAN device. If you are not booting from a LAN device, the boot from LAN options on the **Boot Device Priority** screen should always be set to **Disabled** to eliminate unnecessary delays during the bootup process. This may be done via the **Boot Device Priority** option on the Boot Setup screen of the BIOS Setup Utility.

### Power REQUIREMENTS

The following are typical values:

| Processor<br>Speed                                                         | <u>+5V *</u>               | +12V **                | +3.3V *                | <u>-12V *</u>              |

|----------------------------------------------------------------------------|----------------------------|------------------------|------------------------|----------------------------|

| Intel <sup>®</sup> Pent                                                    | ium <sup>®</sup> 4 Process | sor - 533MHz           | FSB/512K cac           | he:                        |

| 2.8GHz<br>2.4GHz                                                           | 4.95 Amps<br>4.95 Amps     | 4.63 Amps<br>5.00 Amps | 2.50 Amps<br>2.50 Amps | < 100 mAmps<br>< 100 mAmps |

| Intel <sup>®</sup> Celeron <sup>®</sup> Processor - 400MHz FSB/128K cache: |                            |                        |                        |                            |

| 2.5GHz<br>2.0GHz                                                           | 4.95 Amps<br>4.95 Amps     | 4.60 Amps<br>4.20 Amps | 2.50 Amps<br>2.50 Amps | < 100 mAmps<br>< 100 mAmps |

| * From backplane via PICMG connector.                                      |                            |                        |                        |                            |

<sup>\*\*</sup> From ATX12V power supply or equivalent via P24 connector.

**NOTE:** The MX8 requires an *additional* on-board power connector due to the power requirements of the Intel<sup>®</sup> Pentium<sup>®</sup> 4 processor. This 4-pin connector (P24) *requires* +12V from an external power supply that conforms to the ATX12V power specification. The external power supply *must* have a wattage rating of 250W or higher.

The MX8 also requires that +3.3V must be applied to the backplane from the power supply, as specified in the PCI Industrial Computer Manufacturers Group (PICMG<sup>®</sup>) 1.0 Specification. When using a backplane which is not a Trenton product, check with your backplane manufacturer to ensure that the backplane provides +3.3V to the SBC.

# OPERATING TEMPERATURE

Adequate airflow is essential to ensure effective operation of the MX8. The following are operating temperature requirements:

0° C. to 45° C.

0° C. to 45° C. with 250 LFM of airflow (for processors with 800MHz FSB/1M cache and 3.06GHz processor with 533MHz FSB/512K cache)

#### HYPER-THREADING

The factory setting of the **HyperThreading** option in the system BIOS is **Disabled**. This option may be set to **Enabled** for processors which support Hyper-Threading functionality.

Hyper-Threading improves overall performance in many systems designed for multi-processing, high-demand multi-tasking and multi-threaded applications. If you are using a system which can take advantage of Hyper-Threading technology, you may use the BIOS Setup Utility to change the setting of the **HyperThreading** option to **Enabled**. This option is found on the **CPU Configuration** screen in the *Advanced Setup* section of the BIOS Setup Utility.

Intel<sup>®</sup> recommends enabling Hyper-Threading on systems that use Microsoft<sup>®</sup> Windows<sup>®</sup> XP<sup>®</sup> or Linux<sup>®</sup> 2.4.x operating systems.

For systems which use applications and operating systems which cannot take advantage of Hyper-Threading technology, the **HyperThreading** option should remain **Disabled**. Intel recommends disabling Hyper-Threading when using the following operating systems: Microsoft Windows 98<sup>®</sup>, Windows NT<sup>®</sup>, Windows 2000<sup>®</sup>, Windows ME<sup>®</sup>, IBM<sup>®</sup> OS/2<sup>®</sup> and any version of Linux before revision 2.4.x. These operating systems are not optimized for Hyper-Threading technology and some applications may actually experience some performance degradation.

# FOR MORE INFORMATION

For more information on any of these features, refer to the appropriate sections of the *MX8 Technical Reference Manual* (#87-006243-000). The latest revision of this manual may be found on Trenton's website - www.TrentonTechnology.com.

# Chapter 1 Specifications

#### INTRODUCTION

The MX8 full-featured PCI/ISA processors are single board computers (SBCs) which feature the Intel® Pentium® 4 or Intel® Celeron® microprocessor, 400/533/800MHz system bus, ATI Technologies® video interface, support for 2GB DDR memory, PCI Local Bus, cache memory, floppy controller, dual Ultra ATA/100 EIDE interfaces, optional Ultra160 SCSI controller, dual Gigabit Ethernet interfaces, dual Serial ATA ports, two serial ports, parallel port, speaker port and mouse/keyboard port on a single ISA-size card. These single-slot high performance SBCs plug into PICMG® PCI/ISA and PCI-X backplanes and provide full PC compatibility for the system expansion slots.

The MX8-NS models have all of the standard features of the MX8, except they do not include the Adaptec SCSI controller or the Ultra160 SCSI port.

#### **MODELS**

| Model #                                    | Model Name          | <b>Speed</b>      |

|--------------------------------------------|---------------------|-------------------|

| Intel <sup>®</sup> Pentium <sup>®</sup> 4  | Processor - 800MHz  | FSB/1M cache:     |

| 6240-409-xM                                | MX8/3.2G1           | 3.2GHz            |

| 6240-408-xM                                | MX8/3.0G1           | 3.0GHz            |

| 6240-407-xM                                | MX8/2.8G1           | 2.8GHz            |

| Intel <sup>®</sup> Pentium <sup>®</sup> 4  | Processor - 533MHz  | z FSB/512K cache: |

| 6240-108-xM                                | MX8/3.06EN          | 3.06GHz           |

| 6240-107-xM                                | MX8/2.8EN           | 2.8GHz            |

| 6240-106-xM                                | MX8/2.66EN          | 2.66GHz           |

| 6240-105-xM                                | MX8/2.53EN          | 2.53GHz           |

| 6240-104-xM                                | MX8/2.4EN           | 2.4GHz            |

| Intel <sup>®</sup> Celeron <sup>®</sup> Pr | rocessor - 400MHz F | SB/128K cache:    |

| 6240-807-xM                                | MX8/2.5C            | 2.5GHz            |

| 6240-806-xM                                | MX8/2.4C            | 2.4GHz            |

| 6240-805-xM                                | MX8/2.3C            | 2.3GHz            |

| 6240-804-xM                                | MX8/2.2C            | 2.2GHz            |

| 6240-803-xM                                | MX8/2.1C            | 2.1GHz            |

| 6240-802-xM                                | MX8/2.0C            | 2.0GHz            |

| 6240-801-xM                                | MX8/1.8C            | 1.8GHz            |

| 6240-800-xM                                | MX8/1.7C            | 1.7GHz            |

|                                            |                     |                   |

### "No SCSI" Models:

| Intel <sup>®</sup> Pentium <sup>®</sup> 4 | Processor - 800MHz F | SB/1M cache:   |

|-------------------------------------------|----------------------|----------------|

| 6240-429-xM                               | MX8/3.2G1-NS         | 3.2GHz         |

| 6240-428-xM                               | MX8/3.0G1-NS         | 3.0GHz         |

| 6240-427-xM                               | MX8/2.8G1-NS         | 2.8GHz         |

| Intel <sup>®</sup> Pentium <sup>®</sup> 4 | Processor - 533MHz F | SB/512K cache: |

| 6240-128-xM                               | MX8/3.06EN-NS        | 3.06GHz        |

| 6240-127-xM                               | MX8/2.8EN-NS         | 2.8GHz         |

| 6240-126-xM                               | MX8/2.66EN-NS        | 2.66GHz        |

| 6240-125-xM                               | MX8/2.53EN-NS        | 2.53GHz        |

| 6240-124-xM                               | MX8/2.4EN-NS         | 2.4GHz         |

|                                           |                      |                |

# MODELS (CONTINUED)

| Model #                                 | Model Name                    | <b>Speed</b>    |  |  |  |  |

|-----------------------------------------|-------------------------------|-----------------|--|--|--|--|

| "No SCSI" Mo                            | "No SCSI" Models (continued): |                 |  |  |  |  |

| Intel <sup>®</sup> Celeron <sup>®</sup> | Processor - 400MHz            | FSB/128K cache: |  |  |  |  |

| 6240-827-xM                             | MX8/2.5C-NS                   | 2.5GHz          |  |  |  |  |

| 6240-826-xM                             | MX8/2.4C-NS                   | 2.4GHz          |  |  |  |  |

| 6240-825-xM                             | MX8/2.3C-NS                   | 2.3GHz          |  |  |  |  |

| 6240-824-xM                             | MX8/2.2C-NS                   | 2.2GHz          |  |  |  |  |

| 6240-823-xM                             | MX8/2.1C-NS                   | 2.1GHz          |  |  |  |  |

| 6240-822-xM                             | MX8/2.0C-NS                   | 2.0GHz          |  |  |  |  |

MX8/1.8C-NS

MX8/1.7C-NS

where xM indicates memory size (0M = 0MB memory, 64M = 64MB memory, etc.)

### **FEATURES**

• Intel<sup>®</sup> Pentium<sup>®</sup> 4 microprocessor

6240-821-xM

6240-820-xM

3.2GHz, 3.0GHz or 2.8GHz with 1M cache and a 800MHz Front Side Bus (FSB)

1.8GHz

1.7GHz

3.06GHz, 2.8GHz, 2.66GHz, 2.53GHz or 2.4GHz with 512K cache and a 533MHz FSB

or Intel<sup>®</sup> Celeron<sup>®</sup> microprocessor

- 2.5GHz, 2.4GHz, 2.3GHz, 2.2GHz, 2.1GHz, 2.0GHz, 1.8GHz or 1.7GHz with 128K cache and a 400MHz FSB

- Intel 875P chipset with 400/533/800MHz system bus

- PCI Local Bus operating in 32-bit/33MHz mode

- Ultra XGA on-board video interface (ATI Technologies<sup>®</sup>)

- Supports off-board PCI option cards, dual PCI 10/100/1000Base-T Ethernet controllers and optional on-board PCI Ultra160 SCSI controller - Adaptec AIC-7892

- Dual Ethernet interfaces for use with 10/100/1000Base-T networks

- Dual Serial ATA ports support two independent SATA storage devices

- Memory error checking and correction (ECC) support

- Compatible with PCI Industrial Computer Manufacturers Group (PICMG) 1.0 Specification

- Supports up to 2GB of Double Data Rate (DDR) on-board memory

- Floppy drive and dual PCI EIDE Ultra ATA/100 drive interfaces

- Two serial ports and one parallel port

- Dual Universal Serial Bus (USB 2.0) support

- Automatic or manual peripheral configuration

# FEATURES (CONTINUED)

- Watchdog timer

- System hardware monitor

- Full PC compatibility

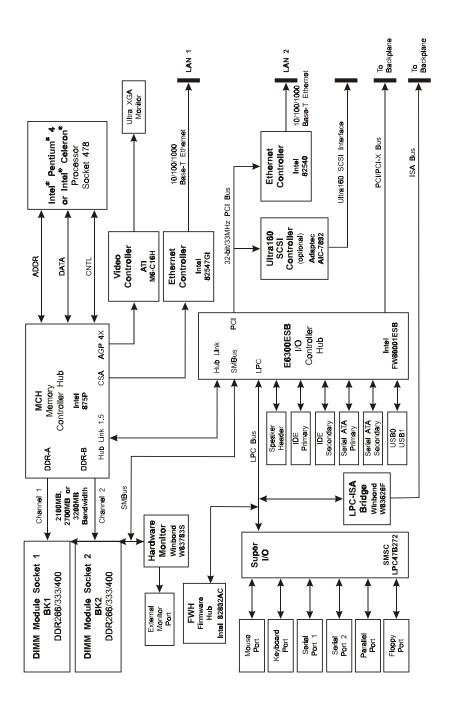

# SBC BLOCK DIAGRAM

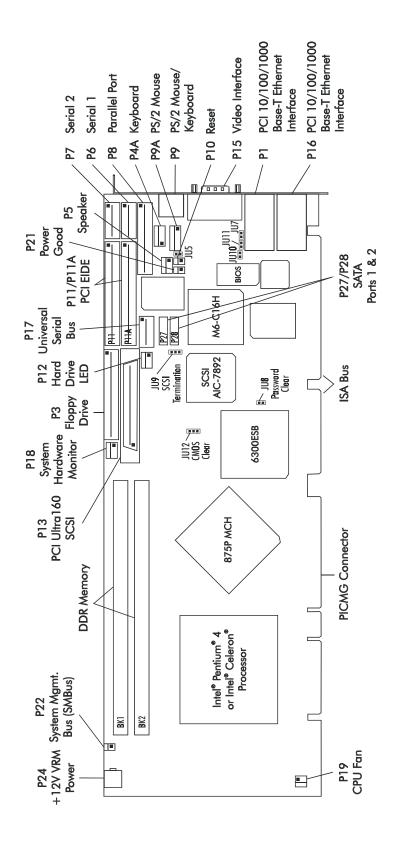

# SBC BOARD LAYOUT

#### **PROCESSOR**

- Intel<sup>®</sup> Pentium<sup>®</sup> 4 microprocessor

- 3.2GHz, 3.0GHz or 2.8GHz with 1M cache and a 800MHz Front Side Bus (FSB)

- 3.06GHz, 2.8GHz, 2.66GHz, 2.53GHz or 2.4GHz with 512K cache and a 533MHz FSB

or Intel<sup>®</sup> Celeron<sup>®</sup> microprocessor

- 2.5GHz, 2.4GHz, 2.3GHz, 2.2GHz, 2.1GHz, 2.0GHz, 1.8GHz or 1.7GHz with 128K cache and a 400MHz FSB

- Processor uses the mPGA 478 packaging

**BUS INTERFACES**

ISA and PCI Local Bus compatible

**DATA PATH**

DDR Memory - 64-bit (per channel)

PCI Bus - 32-bit or 64-bit

PCI-X Bus - 64-bit

BUS SPEED - PCI AND PCI-X PCI - 33MHz or 66MHz PCI-X - 33MHz or 66MHz

BUS SPEED -SYSTEM 400/533/800MHz Front Side Bus

MEMORY INTERFACE Dual Double Data Rate (DDR) memory channels for 2100MB/s, 2700MB/s or 3200MB/s memory bandwidth

**SYSTEM BUS**

The Intel 875P chipset supports the system bus at 400MHz, 533MHz or 800MHz, which provides a higher bandwidth path for transferring data between main memory/chipset and the processor.

**DMA CHANNELS**

The SBC is fully PC compatible with seven DMA channels, each supporting type F transfers.

**INTERRUPTS**

The SBC is fully PC compatible with interrupt steering for PCI plug and play compatibility.

**BIOS (FLASH)**

The BIOS is an AMIBIOS with built-in advanced CMOS setup for system parameters, peripheral management for configuring on-board peripherals and other system parameters. The Flash BIOS resides in the Intel 82802AC Firmware Hub (FWH). The BIOS may be upgraded from floppy disk by pressing **<Ctrl>** + **<Home>** immediately after reset or power-up with the floppy disk in drive A:. Custom BIOSs are available.

**CACHE MEMORY**

The processor includes integrated on-die, 1MB 8-way set associative level two (L2) cache, which implements the Advanced Transfer Cache architecture and runs at the full speed of the processor core. Intel<sup>®</sup> Pentium<sup>®</sup> 4 processors provide either 512K or 1M of L2 cache memory; Intel<sup>®</sup> Celeron<sup>®</sup> processors have a 128K L2 cache.

All processors include a 12K level 1 (L1) Execution Trace Cache. Processors which have 1M of L2 cache memory have a 16K data cache; all other processors have an 8K data cache.

#### NETBURST™ MICRO-ARCHITECTURE

NetBurst micro-architecture defines the techniques Intel uses to enhance the processor's execution of the BIOS, operating system and application software. These techniques include hyper-pipelined technology, a rapid execution engine, advanced dynamic execution, enhanced floating point and multimedia unit and Streaming SIMD Extensions 2 (SSE2). The processor's system bus speed and memory cache are also part of the NetBurst micro-architecture.

Hyper-pipelined technology doubles the pipeline depth inside the processor, which enables more instructions to be loaded, resulting in higher core frequencies. Advanced dynamic execution includes an improved speculative execution algorithm that minimizes processor instruction misdirects and results in faster instruction execution.

The rapid execution engine enables the two arithmetic logic units (ALUs) of the processor to operate at twice the core frequency. Many integer instructions can now execute in half the internal core clock period, resulting in improved software execution speeds.

NetBurst micro-architecture improvements in the floating point and multimedia unit include making the registers 128 bits wide and adding a separate register for moving data.

The SSE2 has 144 instructions which improve performance in secure transactions and multimedia processing. These instructions are used for double-precision floating point, SIMD integer and memory management improvements.

#### **DDR MEMORY**

The Double Data Rate (DDR) memory interface supports up to 2GB of memory and can operate as either a single-channel (64-bit) or dual-channel (128-bit) DDR interface. Each of the channels terminates in a dual in-line memory module (DIMM) socket. Installing two DIMMs doubles the interface bandwidth. The System BIOS automatically detects memory type, size and speed.

The SBC uses industry standard 72-bit wide ECC or 64-bit wide non-ECC gold finger PC2100, PC2700 or PC3200 memory modules in two 184-pin sockets.

**NOTE:** Memory modules can be installed in one or both DIMM sockets. If two modules of different speeds are used, the DIMMs will operate in dual-channel mode at the speed of the slowest DIMM. If the modules are different sizes, they will operate in single-channel mode. Registered DIMMs are *not* supported. All memory modules must have gold contacts.

The SBC supports DIMMs which are PC2100/PC2700/PC3200 compliant and have the following features:

- 184-pin with gold-plated contacts

- ECC (72-bit) or non-ECC (64-bit) DDR memory

- Unbuffered configuration

The following DIMM sizes are supported:

\_\_\_\_\_

| DIMM  |            |           |

|-------|------------|-----------|

| Size  | DIMM Type  | ECC       |

| 64MB  | Unbuffered | 8M x 72   |

| 128MB | Unbuffered | 16M x 72  |

| 256MB | Unbuffered | 32M x 72  |

| 512MB | Unbuffered | 64M x 72  |

| 1GB   | Unbuffered | 128M x 72 |

|       |            |           |

# ERROR CHECKING AND CORRECTION

The memory interface supports ECC modes via BIOS setting for multiple-bit error detection and correction of all errors confined to a single nibble.

### ISA BUS INTERFACE

The ISA bus interface supports legacy ISA slots, but does not support ISA Bus Mastering, 16-bit I/O and 16-bit memory accesses. When a 16-bit access is executed to the ISA bus, the transfer is divided into two 8-bit accesses. If the ISA option card being used only operates in word (16-bit) mode, transfer data will be missed. If the ISA option card supports both byte (8-bit) mode and word mode, the data transfer will be correct, but performance will be reduced.

# PCI-X/PCI LOCAL Bus Interfaces

The SBC is fully compliant with the PCI Local Bus 2.1 Specification. The PCI Local Bus is 32 bits wide and runs at 33MHz. It interfaces to one of the on-board 10/100/1000Base-T Ethernet controllers (Intel 82540) and optional Ultra160 SCSI controller.

The PCI-X/PCI bus interface connects the SBC's I/O Controller Hub directly to the backplane and is capable of running at a 33MHz or 66MHz bus speed. This interface is compliant with the PCI Industrial Computer Manufacturers Group (PICMG) 1.0 Specification.

### UNIVERSAL SERIAL BUS (USB)

The SBC supports two high-speed USB 2.0 ports for data transfers up to 480Mbit/sec. It also supports USB 1.1 devices for data transfers at 12 or 1.5Mbit/sec. The Universal Serial Bus (USB) is an interface allowing for connectivity to many standard PC peripherals via an external port.

### ULTRA XGA INTERFACE

The ATI Technologies M6-C16H video controller enables 2D/3D video acceleration and provides 16MB of integrated video DDR memory. The video controller's DVI compliant 165MHz TMDS transmitter supports pixel resolutions from VGA (640 x 480) up to UXGA (1600 x 1200).

Software drivers are available for most popular operating systems.

### SYSTEM HARDWARE MONITOR

The system hardware monitoring system monitors system voltages, temperature and fan speeds.

The circuitry is based on Winbond's W83783S hardware monitoring IC that is interfaced via the system's SMBus. System voltages of +12V, +5V, +3.3V, +2.5V, VCCORE (processor voltage) and -12V are monitored. Each of these six voltages has programmable "high" and "low" watchdog limits. Also monitored are the processor die temperature and the fan speed associated with the processor's active heatsink thermal solution. Programmable watchdog limits are also associated with fan speed RPMs. When any of these programmed limits are exceeded, monitor software can be used to report the out-of-limit condition.

The System Hardware Monitor connector (P18) provides an external interface for user functionality. Pin assignments for this connector are as follows:

| Pin #/Definition | <u>Description</u>                                                                                                                                                                                                                                                                                                                            |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin 1 - GND      | System Ground                                                                                                                                                                                                                                                                                                                                 |

| Pin 2 - GPO      | General Purpose Output                                                                                                                                                                                                                                                                                                                        |

|                  | Active low open drain output. This multifunction output is controlled by the W38383S's configuration register at offset 40(h) and the control register at 4D(h). It can be used as a general-purpose output or programmed to provide a beep function that can be used as a watchdog warning signal. This output is open drain.                |

| Pin 3 - CI       | Chassis Intrusion Input                                                                                                                                                                                                                                                                                                                       |

|                  | Active low input from an external circuit, which can be used to indicate a chassis intrusion event. This input line is connected directly to the ICH's System Management Interface's INTRUDER# input. It can be set to disable the system if the chassis is open or can be used as a general-purpose input if intruder detection is not used. |

| Pin 4 - OVT      | Over Temperature                                                                                                                                                                                                                                                                                                                              |

|                  | This active low, open drain output can be used to indicate that an over-temperature condition                                                                                                                                                                                                                                                 |

# PCI ETHERNET INTERFACES (DUAL)

The SBC supports two Ethernet interfaces. LAN 1 (P16) is implemented using an Intel 82547GI 10/100/1000Base-T Ethernet PHY and LAN 2 (P1) is implemented using an Intel 82540 10/100/1000Base-T Ethernet controller. Both of these controllers support Gigabit, 10Base-T and 100Base-TX Fast Ethernet modes and are compliant with IEEE 802.3.

The main components of each interface are:

exists.

- Intel 82547GI or Intel 82540 for 10/100/1000-Mb/s media access control (MAC) with PHY, a serial ROM port and a PCI Bus Master interface

- Serial ROM for storing the Ethernet address and the interface configuration and control data

- Integrated RJ-45/Magnetics module connector on the SBC's I/O bracket for direct connection to the network. The connector requires a category 5 (CAT5) unshielded twisted-pair (UTP) 2-pair cable for a 100-Mb/s network connection or a category3 (CAT3) or higher UTP 2-pair cable for a 10-Mb/s network connection. A category 5e (CAT5e) or higher UTP 2-pair cable is recommended for a 1000-Mb/s (Gigabit) network connection.

• Link status and activity LEDs on the I/O bracket for status indication (See *Ethernet LEDs and Connectors* later in this chapter.)

Software drivers are supplied for most popular operating systems.

#### **HUB INTERFACE**

The Intel 875P chipset utilizes a dedicated hub interface connection between the 875P memory controller hub (MCH) and the I/O controller hub (ICH). The purpose of the hub interface is to provide efficient, high-speed communication between chipset components in order to support high-speed I/O applications. It is a parity-protected, 266MB/s point-to-point hub interface and uses an 8-bit 66MHz base clock running at 4x.

### PCI SCSI INTERFACE (OPTIONAL)

The SCSI interface supports Ultra160 SCSI data transfer using Adaptec's AIC-7892 SCSI controller, which supports SCSI data transfer up to 160MB per second. The interface supports up to 15 SCSI devices, complies with the SPI-3 standard and is compatible with both single-ended and Low Voltage Differential (LVD) SCSI I/O. The Ultra160 features of this channel include double-edge clocking, domain validation and cyclical redundancy checking.

Active termination is provided with terminator voltage protected by a self-resetting fuse. A jumper (JU9) is provided to disable the termination (see the *Configuration Jumpers* section later in this chapter). Software drivers are available for most popular operating systems.

The Adaptec SCSISelect Configuration Utility allows you to view and/or change the default configuration settings for the Ultra160 SCSI adapter. You may press **<Ctrl>** + **<A>** to invoke the configuration utility.

### SERIAL ATA/150 PORTS (DUAL)

The primary and secondary Serial ATA (SATA) ports on the MX8 comply with the SATA 1.0 specification and support two independent SATA storage devices such as hard disks and CD-RW devices. SATA technology provides lower pin counts, reduced signaling voltages, simplified cabling, CRC error detection and hot-plug support. SATA produces higher performance interfacing by providing data transfer rates up to 150MB per second on each port.

# PCI ENHANCED IDE INTERFACES (DUAL)

Dual high performance PCI Bus Master EIDE interfaces are capable of supporting two IDE disk drives each in a master/slave configuration. The interfaces support Ultra ATA/100 with synchronous ATA mode transfers up to 100MB per second. Ultra ATA/100 cables must be used with Ultra ATA/100 drives.

# FLOPPY DRIVE INTERFACE

The SBC supports two floppy disk drives. Drives can be 360K to 2.88MB, in any combination.

# SERIAL INTERFACE

Two high-speed FIFO (16C550) serial ports with independently programmable baud rates are supported. The IRQ for each serial port has BIOS selectable addressing.

### ENHANCED PARALLEL INTERFACE

The SBC provides a PC/AT compatible bidirectional parallel port and supports enhanced parallel port (EPP) mode and extended capabilities port (ECP) mode. The ECP mode is IEEE 1284 compliant. The IRQ for the parallel port has BIOS selectable addressing.

# PS/2 Mouse Interface

The SBC is compatible with a PS/2-type mouse. The mouse connection can be made by using either the PS/2 mouse header or the bracket mounted mouse/keyboard mini DIN connector. The mouse may be connected directly to the mini DIN connector or to the "mouse" side of the "Y" adapter. Mouse voltage is protected by a self-resetting fuse.

### KEYBOARD INTERFACE

The SBC is compatible with an AT-type keyboard. The keyboard connection can be made by using either the keyboard header or the "keyboard" side of the "Y" adapter plugged into the bracket mounted mouse/keyboard mini DIN connector. Keyboard voltage is protected by a self-resetting fuse.

#### **WATCHDOG TIMER**

The watchdog timer is a hardware timer which resets the SBC if the timer is not refreshed by software periodically. The timer is typically used to restart a system in which an application becomes hung on an external event. When the application is hung, it no longer refreshes the timer. The watchdog timer then times out and resets the SBC.

The watchdog timer (WDT) is integrated into the E6300ESB I/O Controller Hub (ICH) and provides a resolution that ranges from 1 msecond to 10 minutes. The WDT provides a two-stage timer implementation: the first stage can be used to generate an IRQ, SMI or SCI interrupt after the programmed time interval has expired; the second stage can be used to generate a hard system reset.

The WDT uses a 35-bit down-counter, which is loaded with the value from the first preload register. The timer is then enabled and starts its down counting, which is the first stage. When the host fails to reload the WDT before the 35-bit down-counter reaches zero, the WDT generates an internal interrupt. After the interrupt is generated, the WDT loads the value from the second preload register into the 35-bit down-counter and starts counting down. The WDT is now in the second stage. If the host fails to reload the WDT before the second stage times out, a system RESET is generated.

# POWER FAIL DETECTION

A hardware reset is issued when any of the monitored voltages drops below its specified nominal low voltage limit.

The monitored voltages and their nominal low limits are listed below.

| Monitored Voltage | Nominal<br><u>Low Limit</u> | Voltage Source      |

|-------------------|-----------------------------|---------------------|

| +5V               | 4.5 volts                   | System Power Supply |

| +3.3V             | 2.97 volts                  | System Power Supply |

| +1.2V             | 1.056 volts                 | On-Board Regulator  |

| +1.25V            | 1.1 volt                    | On-Board Regulator  |

| +2.5V             | 2.452 volts                 | On-Board Regulator  |

### **BATTERY**

A built-in lithium battery is provided, for ten years of data retention for CMOS memory.

**CAUTION:** There is a danger of explosion if the battery is incorrectly replaced. Replace it only with the same or equivalent type recommended by the manufacturer. Dispose of used batteries according to the manufacturer's instructions.

# POWER REQUIREMENTS

The following are typical values:

| Processor<br>Speed       | <u>+5V *</u>              | +12V **                | +3.3V *                | <u>-12V *</u>              |

|--------------------------|---------------------------|------------------------|------------------------|----------------------------|

| Intel <sup>®</sup> Penti | um <sup>®</sup> 4 Process | sor - 533MHz           | FSB/512K cac           | he:                        |

| 2.8GHz<br>2.4GHz         | 4.95 Amps<br>4.95 Amps    | 4.63 Amps<br>5.00 Amps | 2.50 Amps<br>2.50 Amps | < 100 mAmps<br>< 100 mAmps |

| Intel <sup>®</sup> Celer | on <sup>®</sup> Processor | - 400MHz FS            | B/128K cache           | :                          |

| 2.5GHz<br>2.0GHz         | 4.95 Amps<br>4.95 Amps    | 4.60 Amps<br>4.20 Amps | 2.50 Amps<br>2.50 Amps | < 100 mAmps<br>< 100 mAmps |

<sup>\*</sup> From backplane via PICMG connector.

**NOTE:** The MX8 requires an *additional* on-board power connector due to the power requirements of the Intel<sup>®</sup> Pentium<sup>®</sup> 4 processor. This 4-pin connector (P24) *requires* +12V from an external power supply that conforms to the ATX12V power specification. The external power supply *must* have a wattage rating of 250W or higher.

The MX8 also requires that +3.3V must be applied to the backplane from the power supply, as specified in the PCI Industrial Computer Manufacturers Group (PICMG<sup>®</sup>) 1.0 Specification. When using a backplane which is not a Trenton product, check with your backplane manufacturer to ensure that the backplane provides +3.3V to the SBC.

# TEMPERATURE/ ENVIRONMENT

**Operating Temperature:** 0° C. to 45° C.

0° C. to 45° C. with 250 LFM of airflow

(for processors with 800MHz FSB/1M cache and 3.06GHz processor with 533MHz FSB/512K cache)

**Storage Temperature:** - 40° C. to 70° C.

**Humidity:** 5% to 90% non-condensing

<sup>\*\*</sup> From ATX12V power supply or equivalent via P24 connector.

# CONFIGURATION JUMPERS

The setup of the configuration jumpers on the SBC is described below. \* indicates the default value of each jumper.

**NOTE:** For two-position jumpers (3-post), "TOP" is toward the memory sockets; "BOTTOM" is toward the edge fingers.

Jumper

**Description**

#### JU5/JU7

### Speed LED - LAN 1/LAN 2

These jumpers are used in conjunction with the Link/Speed LEDs for LAN 1 (JU5) and LAN 2 (JU7). The LEDs are located on the SBC's LAN connectors. For further information, see the *Ethernet LEDs and Connectors* section below.

Install to use the Link/Speed LED to indicate that the Ethernet interface has a valid link at either 1000-Mb/s or 100-Mb/s.

Green = valid link at 1000-Mb/s \* Orange = valid link at 100-Mb/s

Remove to use the Link/Speed LED to indicate that the Ethernet interface has a valid link at either 100-Mb/s or 10-Mb/s.

Orange = valid link at 100-Mb/s Green = valid link at 10-Mb/s

#### JU8 Password Clear

Install for one power-up cycle to reset the password to the default (null password).

Remove for normal operation. \*

#### JU9 SCSI Termination

This jumper may be used to enable or disable on-board active termination for the Ultra160 SCSI interface.

Install on the TOP to enable active termination. \* Install on the BOTTOM to allow the AIC-7892 to control termination.

Remove to disable active termination.

# CONFIGURATION JUMPERS (CONTINUED)

### <u>Jumper</u> <u>Description</u>

# JU10/JU11 System Flash ROM Operational Modes

The Flash ROM has two programmable sections: the Boot Block for "flashing" in the BIOS and the Main Block for the executable BIOS and PnP parameters. Normally only the Main Block is updated when a new BIOS is flashed into the system.

|                            | <u>JU10</u> | <u>JU11</u> |

|----------------------------|-------------|-------------|

| All Blocks Write Enabled   | Remove *    | Remove *    |

| Boot Block Write Protected | Install     | Remove      |

| Block 2-16 Write Protected | Remove      | Install     |

#### JU12 CMOS Clear

Install on the TOP to operate. \* Install on the BOTTOM to clear.

**NOTE:** The CMOS Clear jumper works on power-up. To clear the CMOS, power down the system, install the jumper, then turn the power back on. Wait for at least two seconds and turn the power off. Then remove the jumper and turn the power on. When AMIBIOS displays the "CMOS Settings Wrong" message, press F1 to go into the BIOS Setup Utility, where you may reenter your desired BIOS settings, load optimal defaults or load failsafe defaults.

# ETHERNET LEDS AND CONNECTORS

Each Ethernet interface has two LEDs for status indication and an RJ-45 network connector.

| LED/Connector | <u>Description</u>                                                                                                         |

|---------------|----------------------------------------------------------------------------------------------------------------------------|

| Activity LED  | Orange LED which indicates network activity. This is the upper LED on the LAN connector (i.e., toward the memory sockets). |

| Off           | Indicates there is no current network transmit or receive activity.                                                        |

| On (flashing) | Indicates network transmit or receive activity.                                                                            |

| ETHERNET LEDS  |

|----------------|

| AND CONNECTORS |

| (CONTINUED)    |

| LED/Connector  | Description                                                                                                                                                       |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Link/Speed LED | Bi-color (green/orange) LED which identifies the link status and connection speed. This is the lower LED on the LAN connector (i.e., toward the edge connectors). |

| Green          | Indicates a valid link at either 1000-Mb/s or 10-Mb/s, depending on the setting of the associated Speed LED jumper (JU5 or JU7).                                  |

| Orange         | Indicates a valid link at 100-Mb/s, regardless of the setting of the associated Speed LED jumper (JU5 or JU7).                                                    |

|                | <b>NOTE:</b> For further information on the Speed LED jumpers, see the <i>Configuration Jumpers</i> section earlier in this chapter.                              |

RJ-45 Network Connector The RJ-45 network connector requires a category 5 (CAT5) unshielded twisted-pair (UTP) 2-pair cable for a 100-Mb/s network connection or a category 3 (CAT3) or higher UTP 2-pair cable for a 10-Mb/s network connection. A category 5e (CAT5e) or higher UTP 2-pair cable is recommended for a 1000-Mb/s (Gigabit) network connection.

### SYSTEM BIOS SETUP UTILITY

The System BIOS is an AMIBIOS with a ROM-resident setup utility. The BIOS Setup Utility allows you to select to the following categories of options:

- Main Menu

- Advanced Setup

- PCIPnP Setup

- Boot Setup

- · Security Setup

- · Chipset Setup

- Exit

Each of these options allows you to review and/or change various setup features of your system. Details are provided in the following chapters of this manual.

# **CONNECTORS**

**NOTE:** Pin 1 on the connectors is indicated by the square pad on the PCB.

#### P1 -10/100/1000Base-T Ethernet Connector - LAN 2

8 pin shielded RJ-45 connector, Belfuse #0826-1X1T-23

| <u>Pin</u> | <u>Signal</u> |

|------------|---------------|

| 1          | TRP1+         |

| 2          | TRP1-         |

| 3          | TRP2+         |

| 4          | TRP3+         |

5 TRP3-6 TRP2-

7 TRP4+

TRP4-

#### **P3 Floppy Drive Connector**

34 pin dual row header, Amp #103308-7

| <u>Pin</u> | <u>Signal</u> | <u>Pin</u> | <u>Signal</u>   |

|------------|---------------|------------|-----------------|

| 1          | Gnd           | 2          | N-RPM           |

| 3          | Gnd           | 4          | NC              |

| 5          | Gnd           | 6          | D-Rate0         |

| 7          | Gnd           | 8          | P-Index         |

| 9          | Gnd           | 10         | N-Motoron 1     |

| 11         | Gnd           | 12         | N-Drive Sel2    |

| 13         | Gnd           | 14         | N-Drive Sel1    |

| 15         | Gnd           | 16         | N-Motoron 2     |

| 17         | Gnd           | 18         | N-Dir           |

| 19         | Gnd           | 20         | N-Stop Step     |

| 21         | Gnd           | 22         | N-Write Data    |

| 23         | Gnd           | 24         | N-Write Gate    |

| 25         | Gnd           | 26         | P-Track 0       |

| 27         | Gnd           | 28         | P-Write Protect |

| 29         | Gnd           | 30         | N-Read Data     |

| 31         | Gnd           | 32         | N-Side Select   |

| 33         | Gnd           | 34         | Disk Chng       |

#### P4A -**Keyboard Header**

5 pin single row header, Amp #640456-5

| <u>Pin</u> | <u>Signal</u> |

|------------|---------------|

| 1          | Kbd Clock     |

| 2          | Kbd Data      |

3 Key

4 Kbd Gnd

Kbd Power (+5V fused) with self-resetting fuse

# P5 - Speaker Port Connector

4 pin single row header, Amp #640456-4

# Pin Signal

- 1 Speaker Data

- 2 Key

- 3 Gnd

- 4 +5V

### P6 - Serial Port 1 Connector

10 pin dual row header, Amp #103308-1

| <u>Pin</u> | <u>Signal</u>         | <u>Pin</u> | <u>Signal</u>     |

|------------|-----------------------|------------|-------------------|

| 1          | Carrier Detect        | 2          | Data Set Ready-I  |

| 3          | Receive Data-I        | 4          | Request to Send-O |

| 5          | Transmit Data-O       | 6          | Clear to Send-I   |

| 7          | Data Terminal Ready-O | 8          | Ring Indicator-I  |

| 9          | Signal Gnd            | 10         | NC                |

# P7 - Serial Port 2 Connector

10 pin dual row header, Amp #103308-1

| <u>Pin</u> | <u>Signal</u>         | <u>Pin</u> | <u>Signal</u>     |

|------------|-----------------------|------------|-------------------|

| 1          | Carrier Detect        | 2          | Data Set Ready-I  |

| 3          | Receive Data-I        | 4          | Request to Send-O |

| 5          | Transmit Data-O       | 6          | Clear to Send-I   |

| 7          | Data Terminal Ready-O | 8          | Ring Indicator-I  |

| 9          | Signal Gnd            | 10         | NC                |

# P8 - Parallel Port Connector

26 pin dual row header, Amp #103308-6

| <u>Pin</u> | <u>Signal</u> | <u>Pin</u> | <u>Signal</u> |

|------------|---------------|------------|---------------|

| 1          | Strobe        | 2          | Auto Feed XT  |

| 3          | Data Bit 0    | 4          | Error         |

| 5          | Data Bit 1    | 6          | Init          |

| 7          | Data Bit 2    | 8          | Slct In       |

| 9          | Data Bit 3    | 10         | Gnd           |

| 11         | Data Bit 4    | 12         | Gnd           |

| 13         | Data Bit 5    | 14         | Gnd           |

| 15         | Data Bit 6    | 16         | Gnd           |

| 17         | Data Bit 7    | 18         | Gnd           |

| 19         | ACK           | 20         | Gnd           |

| 21         | Busy          | 22         | Gnd           |

| 23         | Paper End     | 24         | Gnd           |

| 25         | Slct          | 26         | NC            |

# P9 - PS/2 Mouse and Keyboard Connector

6 pin mini DIN, Kycon #KMDG-6S-B4T

# Pin Signal

- 1 Ms Data

- 2 Kbd Data

- 3 Gnd

- 4 Power (+5V fused) with self-resetting fuse

- 5 Ms Clock

- 6 Kbd Clock

### P9A - PS/2 Mouse Header

6 pin single row header, Amp #640456-6

# Pin Signal

- 1 Ms Data

- 2 Reserved

- 3 Gnd

- 4 Power (+5V fused) with self-resetting fuse

- 5 Ms Clock

- 6 Reserved

### P10 - External Reset Connector

2 pin single row header, Amp #640456-2

# Pin Signal

- 1 External Reset In (Low Active)

- 2 Gnd

# P11 - Primary IDE Hard Drive Connector

40 pin dual row header, 3M #30340-6002HB

| <u>Pin</u> | <u>Signal</u> | <u>Pin</u> | <u>Signal</u> |

|------------|---------------|------------|---------------|

| 1          | Reset         | 2          | Gnd           |

| 3          | Data 7        | 4          | Data 8        |

| 5          | Data 6        | 6          | Data 9        |

| 7          | Data 5        | 8          | Data 10       |

| 9          | Data 4        | 10         | Data 11       |

| 11         | Data 3        | 12         | Data 12       |

| 13         | Data 2        | 14         | Data 13       |

| 15         | Data 1        | 16         | Data 14       |

| 17         | Data 0        | 18         | Data 15       |

| 19         | Gnd           | 20         | NC            |

| 21         | DRQ 0         | 22         | Gnd           |

| 23         | IOW           | 24         | Gnd           |

| 25         | IOR           | 26         | Gnd           |

| 27         | IORDY         | 28         | SELPDP        |

| 29         | DACK 0        | 30         | Gnd           |

|            |               |            |               |

# P11 - Primary IDE Hard Drive Connector (continued)

| <u>Pin</u> | <u>Signal</u> | <u>Pin</u> | <u>Signal</u> |

|------------|---------------|------------|---------------|

| 31         | IRQ 14        | 32         | NC            |

| 33         | Add 1         | 34         | PCBL DET *    |

| 35         | Add 0         | 36         | Add 2         |

| 37         | CS 1P         | 38         | CS 3P         |

| 39         | IDEACTP       | 40         | Gnd           |

# P11A - Secondary IDE Hard Drive Connector

40 pin dual row header, 3M #30340-6002HB

| <u>Pin</u> | <u>Signal</u> | <u>Pin</u> | <u>Signal</u> |

|------------|---------------|------------|---------------|

| 1          | Reset         | 2          | Gnd           |

| 3          | Data 7        | 4          | Data 8        |

| 5          | Data 6        | 6          | Data 9        |

| 7          | Data 5        | 8          | Data 10       |

| 9          | Data 4        | 10         | Data 11       |

| 11         | Data 3        | 12         | Data 12       |

| 13         | Data 2        | 14         | Data 13       |

| 15         | Data 1        | 16         | Data 14       |

| 17         | Data 0        | 18         | Data 15       |

| 19         | Gnd           | 20         | NC            |

| 21         | DRQ 1         | 22         | Gnd           |

| 23         | IOW           | 24         | Gnd           |

| 25         | IOR           | 26         | Gnd           |

| 27         | IORDY         | 28         | SELPDS        |

| 29         | DACK 1        | 30         | Gnd           |

| 31         | IRQ 15        | 32         | NC            |

| 33         | Add 1         | 34         | SCBL DET *    |

| 35         | Add 0         | 36         | Add 2         |

| 37         | CS 1S         | 38         | CS 3S         |

| 39         | IDEACTS       | 40         | Gnd           |

|            |               |            |               |

<sup>\*</sup> For ATA/66 and ATA/100 drives, which should be set for Cable Select for proper speed operation. If other drives are detected, pin definition is Gnd.

### P12 - Hard Drive LED Connector

4 pin single row header, Amp #640456-4

| <u> Pın</u> | Signal |

|-------------|--------|

| 1           | LED +  |

| 2           | LED -  |

| 3           | LED -  |

| 4           | LED +  |

# P13 - Ultra160 SCSI Connector

68 pin high density connector, Amp #749069-7

| <u>Pin</u> | <u>Signal</u> | <u>Pin</u> | <u>Signal</u> |

|------------|---------------|------------|---------------|

| 1          | SCD12         | 35         | SCD#12        |

| 2          | SCD13         | 36         | SCD#13        |

| 3          | SCD14         | 37         | SCD#14        |

| 4          | SCD15         | 38         | SCD#15        |

| 5          | SCDPH         | 39         | SCDPH#        |

| 6          | SCD0          | 40         | SCD#0         |

| 7          | SCD1          | 41         | SCD#1         |

| 8          | SCD2          | 42         | SCD#2         |

| 9          | SCD3          | 43         | SCD#3         |

| 10         | SCD4          | 44         | SCD#4         |

| 11         | SCD5          | 45         | SCD#5         |

| 12         | SCD6          | 46         | SCD#6         |

| 13         | SCD7          | 47         | SCD#7         |

| 14         | SCDPL         | 48         | SCDPL#        |

| 15         | Gnd           | 49         | Gnd           |

| 16         | DIFSENSE      | 50         | Gnd           |

| 17         | TERMPWR       | 51         | TERMPWR       |

| 18         | TERMPWR       | 52         | TERMPWR       |

| 19         | NC            | 53         | NC            |

| 20         | Gnd           | 54         | Gnd           |

| 21         | SCATN         | 55         | SCATN#        |

| 22         | Gnd           | 56         | Gnd           |

| 23         | SCBSY         | 57         | SCBSY#        |

| 24         | SCACK         | 58         | SCACK#        |

| 25         | SCRST         | 59         | SCRST#        |

| 26         | SCMSG         | 60         | SCMSG#        |

| 27         | SCSEL         | 61         | SCSEL#        |

| 28         | SCCD          | 62         | SCCD#         |

| 29         | SCREQ         | 63         | SCREQ#        |

| 30         | SCIO          | 64         | SCIO#         |

| 31         | SCD8          | 65         | SCD#8         |

| 32         | SCD9          | 66         | SCD#9         |

| 33         | SCD10         | 67         | SCD#10        |

| 34         | SCD11         | 68         | SCD#11        |

|            |               |            |               |

# P15 - Video Interface Connector

15 pin connector, Amp #1-1470250-3

|            |               | Pin | Signal |            |               |

|------------|---------------|-----|--------|------------|---------------|

| <u>Pin</u> | <u>Signal</u> |     | -      | <u>Pin</u> | <u>Signal</u> |

|            | D 1           | 6   | Gnd    |            | NG            |

| 1          | Red           | 7   | Gnd    | 11         | NC            |

| 2          | Green         | /   | Gila   | 12         | EEDI          |

| _          | Green         | 8   | Gnd    | 12         | LLDI          |

| 3          | Blue          |     |        | 13         | HSYNC         |

|            |               | 9   | +5V    |            |               |

| 4          | NC            | 1.0 | G 1    | 14         | VSYNC         |

|            |               | 10  | Gnd    |            |               |

| 5          | Gnd           |     |        | 15         | EECS          |

# P16 - 10/100/1000Base-T Ethernet Connector - LAN 1

8 pin shielded RJ-45 connector, Belfuse #0826-1X1T-23

| <u>Pin</u> | <u>Signal</u> |

|------------|---------------|

| 1          | TRP1+         |

| 2          | TRP1-         |

| 3          | TRP2+         |

| 4          | TRP3+         |

| 5          | TRP3-         |

| 6          | TRP2-         |

| 7          | TRP4+         |

| 8          | TRP4-         |

# P17 - Universal Serial Bus (USB) Connector

8 pin dual row header, Molex #702-46-0821 (+5V fused with self-resetting fuses)

| <u>Pin</u> | <u>Signal</u> | <u>Pin</u> | Signal   |

|------------|---------------|------------|----------|

| 1          | +5V-USB0      | 2          | +5V-USB1 |

| 3          | USB0-         | 4          | USB1-    |

| 5          | USB0+         | 6          | USB1+    |

| 7          | Gnd-USB0      | 8          | Gnd-USB1 |

# P18 - System Hardware Monitor Connector

4 pin single row header, Amp #640456-4

| <u>Pin</u> | <u>Signal</u>                |

|------------|------------------------------|

| 1          | Gnd                          |

| 2          | GPO (General Purpose Output) |

| 3          | CI (Chassis Intrusion Input) |

| 4          | OVT (Over Temperature)       |

### P19 - CPU Fan

3 pin single row header, Molex #22-23-2031

# Pin Signal

- 1 Gnd

- 2 +12V

- 3 FanTach

### P21 - Power Good LED

2 pin single row header, Amp #640456-2

# Pin Signal

- 1 LED -

- 2 LED +

# P22 - System Management Bus Connector

2 pin single row header, Amp #640456-2

# Pin Signal

- 1 SMB Clock

- 2 SMB Data

# P24 - +12V VRM Power Input

4 pin header, Molex #39-29-3046

### Pin Signal

- 1 Gnd

- 2 Gnd

- 3 +12V

- 4 +12V

### P27 - SATA Port 1

7 pin vertical connector, Molex #67491-0031

# Pin Signal

- 1 Gnd

- 2 TX+

- 3 TX-

- 4 Gnd

- 5 RX-

- 6 RX+

- 7 Gnd

# P28 - SATA Port 2

7 pin vertical connector, Molex #67491-0031

| <u>Pin</u> | Signal |

|------------|--------|

| 1          | Gnd    |

| 2          | TX+    |

| 3          | TX-    |

| 4          | Gnd    |

| 5          | RX-    |

| 6          | RX+    |

| 7          | Gnd    |

This page intentionally left blank.

# Chapter 2 ISA/PCI Reference

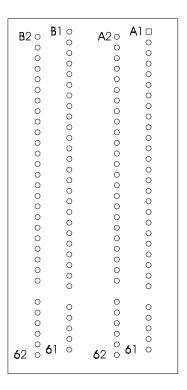

ISA BUS PIN NUMBERING

62-pin ISA Bus

Connector

D1 0 C1 0

D1 0 C1 0

Connector

Component Side of Board

# ISA BUS PIN ASSIGNMENTS

The following tables summarize pin assignments for the Industry Standard Architecture (ISA) Bus connectors.

| I/O Pin | Signal Name | I/O | I/O Pin | Signal Name | I/O    |

|---------|-------------|-----|---------|-------------|--------|

| A1      | IOCHK#      | 1   | B1      | Gnd         | Ground |

| A2      | D7          | I/O | B2      | RESDRV      | 0      |

| A3      | D6          | I/O | В3      | +5V         | Power  |

| A4      | D5          | I/O | B4      | IRQ9        | 1      |

| A5      | D4          | I/O | B5      | -5V         | Power  |

| A6      | D3          | I/O | B6      | DRQ2        | 1      |

| A7      | D2          | I/O | B7      | -12V        | Power  |

| A8      | D1          | I/O | B8      | NOWS#       | I      |

| A9      | D0          | I/O | В9      | +12V        | Power  |

| A10     | CHRDY       | I   | B10     | Gnd         | Ground |

| A11     | AEN         | 0   | B11     | SMWTC#      | 0      |

| A12     | SA19        | I/O | B12     | SMRDC#      | 0      |

| A13     | SA18        | I/O | B13     | IOWC#       | I/O    |

| A14     | SA17        | I/O | B14     | IORC#       | I/O    |

| A15     | SA16        | I/O | B15     | DAK3#       | 0      |

| A16     | SA15        | I/O | B16     | DRQ3        | I      |

| A17     | SA14        | I/O | B17     | DAK1#       | 0      |

| A18     | SA13        | I/O | B18     | DRQ1        | I      |

| A19     | SA12        | I/O | B19     | REFRESH#    | I/O    |

| A20     | SA11        | I/O | B20     | BCLK        | 0      |

| A21     | SA10        | I/O | B21     | IRQ7        | I      |

| A22     | SA9         | I/O | B22     | IRQ6        | 1      |

| A23     | SA8         | I/O | B23     | IRQ5        | 1      |

| A24     | SA7         | I/O | B24     | IRQ4        | I      |

| A25     | SA6         | I/O | B25     | IRQ3        | 1      |

| A26     | SA5         | I/O | B26     | DAK2#       | 0      |

| A27     | SA4         | I/O | B27     | T-C         | 0      |

| A28     | SA3         | I/O | B28     | BALE        | 0      |

| A29     | SA2         | I/O | B29     | +5V         | Power  |

| A30     | SA1         | I/O | B30     | OSC         | 0      |

| A31     | SA0         | I/O | B31     | Gnd         | Ground |

| I/O Pin | Signal Name | I/O | I/O Pin | Signal Name | I/O    |

|---------|-------------|-----|---------|-------------|--------|

| C1      | SBHE#       | I/O | D1      | M16#        | I      |

| C2      | LA23        | I/O | D2      | IO16#       | 1      |

| C3      | LA22        | I/O | D3      | IRQ10       | I      |

| C4      | LA21        | I/O | D4      | IRQ11       | I      |

| C5      | LA20        | I/O | D5      | IRQ12       | I      |

| C6      | LA19        | I/O | D6      | IRQ15       | I      |

| C7      | LA18        | I/O | D7      | IRQ14       | I      |

| C8      | LA17        | I/O | D8      | DAK0#       | 0      |

| C9      | MRDC#       | I/O | D9      | DRQ0        | I      |

| C10     | MWTC#       | I/O | D10     | DAK5#       | 0      |

| C11     | D8          | I/O | D11     | DRQ5        | I      |

| C12     | D9          | I/O | D12     | DAK6#       | 0      |

| C13     | D10         | I/O | D13     | DRQ6        | I      |

| C14     | D11         | I/O | D14     | DAK7#       | 0      |

| C15     | D12         | I/O | D15     | DRQ7        | 1      |

| C16     | D13         | I/O | D16     | +5V         | Power  |

| C17     | D14         | I/O | D17     | Master16#   | ı      |

| C18     | D15         | I/O | D18     | Gnd         | Ground |

# ISA BUS SIGNAL DESCRIPTIONS

The following is a description of the ISA Bus signals. All signal lines are TTL-compatible.

#### AEN (O)

Address Enable (AEN) is used to degate the microprocessor and other devices from the I/O channel to allow DMA transfers to take place. When this line is active, the DMA controller has control of the address bus, the data-bus Read command lines (memory and I/O), and the Write command lines (memory and I/O).

#### BALE (O) (Buffered)

Address Latch Enable (BALE) is provided by the bus controller and is used on the system board to latch valid addresses and memory decodes from the microprocessor. It is available to the I/O channel as an indicator of a valid microprocessor or DMA address (when used with AEN). Microprocessor addresses SA[19::0] are latched with the falling edge of BALE. BALE is forced high during DMA cycles.

#### BCLK (O)

BCLK is the system clock. The clock has a 50% duty cycle. This signal should only be used for synchronization. It is not intended for uses requiring a fixed frequency.

#### CHRDY (I)

I/O Channel Ready (CHRDY) is pulled low (not ready) by a memory or I/O device to lengthen I/O or memory cycles. Any slow device using this line should drive it low immediately upon detecting its valid address and a Read or Write command. Machine cycles are extended by an integral number of clock cycles. This signal should be held low for no more than 2.5 microseconds.

#### D[15::0] (I/O)

Data signals D[15::0] provide bus bits 15 through 0 for the microprocessor, memory, and I/O devices. D15 is the most-significant bit and D0 is the least-significant bit. All 8-bit devices on the I/O channel should use D[7::0] for communications to the microprocessor. The 16-bit devices will use D[15::0]. To support 8-bit devices, the data on D[15::8] will be gated to D[7::0] during 8-bit transfers to these devices. 16-bit microprocessor transfers to 8-bit devices will be converted to two 8-bit transfers.

### DAK[7::5]#, DAK[3::0]# (O)

DMA Acknowledge DAK[7::5]# and DAK[3::0]# are used to acknowledge DMA requests DRQ[7::5] and DRQ[3::0]. They are active low.

## DRQ[7::5], DRQ[3::0] (I)

DMA Requests DRQ[7::5] and DRQ[3::0] are asynchronous channel requests used by peripheral devices and the I/O channel microprocessors to gain DMA service (or control of the system). They are prioritized, with DRQ0 having the highest priority and DRQ7 having the lowest. A request is generated by bringing a DRQ line to an active level. A DRQ line must be held high until the corresponding DMA Request Acknowledge (DAK) line goes active. DRQ[3::0] will perform 8-bit DMA transfers; DRQ[7::5] will perform 16-bit transfers.

#### IO16# (I)

I/O 16-bit Chip Select (IO16#) signals the system board that the present data transfer is a 16-bit, 1 wait-state, I/O cycle. It is derived from an address decode. IO16# is active low and should be driven with an open collector or tri-state driver capable of sinking 20 mAmps.

#### IOCHK# (I)

I/O Channel Check (IOCHK#) provides the system board with parity (error) information about memory or devices on the I/O channel. When this signal is active, it indicates an uncorrectable system error.

#### IORC# (I/O)

I/O Read (IORC#) instructs an I/O device to drive its data onto the data bus. It may be driven by the system microprocessor or DMA controller, or by a microprocessor or DMA controller resident on the I/O channel. This signal is active low.

#### IOWC# (I/O)

I/O Write (IOWC#) instructs an I/O device to read the data on the data bus. It may be driven by any microprocessor or DMA controller in the system. This signal is active low.

#### IRQ[15::14], IRQ[12::9], IRQ[7::3] (I)

Interrupt Requests IRQ[15::14], IRQ[12::9] and IRQ[7::3] are used to signal the microprocessor that an I/O device needs attention. The interrupt requests are prioritized, with IRQ[15::14] and IRQ[12::9] having the highest priority (IRQ9 is the highest) and IRQ[7::3] having the lowest priority (IRQ7 is the lowest). An interrupt request is generated when an IRQ line is raised from low to high. The line must be held high until the microprocessor acknowledges the interrupt request (Interrupt Service routine).

#### LA[23::17] (I/O)

These signals (unlatched) are used to address memory and I/O devices within the system. They give the system up to 16MB of addressability. These signals are valid when BALE is high. LA[23::17] are not latched during microprocessor cycles and therefore do not stay valid for the whole cycle. Their purpose is to generate memory decodes for 1 wait-state memory cycles. These decodes should be latched by I/O adapters on the falling edge of BALE. These signals also may be driven by other microprocessors or DMA controllers that reside on the I/O channel.

## M16# (I)

M16# Chip Select signals the system board if the present data transfer is a 1<N>wait-state, 16-bit, memory cycle. It must be derived from the decode of LA[23::17]. M16# should be driven with an open collector or tri-state driver capable of sinking 20 mAmps.

### Master16# (I)

Master16# is used with a DRQ line to gain control of the system. A processor or DMA controller on the I/O channel may issue a DRQ to a DMA channel in cascade mode and receive a DAK#. Upon receiving the DAK#, an I/O microprocessor may pull Master16# low, which will allow it to control the system address, data, and control lines (a condition known as tri-state). After Master16# is low, the I/O microprocessor must wait one system clock period before driving the address and data lines, and two clock periods before issuing a Read or Write command. If this signal is held low for more than 15<N>microseconds, system memory may be lost because of a lack of refresh.

#### NOWS# (I)

The No Wait State (NOWS#) signal tells the microprocessor that it can complete the present bus cycle without inserting any additional wait cycles. In order to run a memory cycle to a 16-bit device without wait cycles, NOWS# is derived from an address decode gated with a Read or Write command. In order to run a memory cycle to an 8-bit device with a minimum of two wait states, NOWS# should be driven active on system clock after the Read or Write command is active gated with the address decode for the device. Memory Read and Write commands to a 8-bit device are active on the falling edge of the system clock. NOWS# is active low and should be driven with an open collector or tri-state driver capable of sinking 20 mAmps.

#### OSC (O)

Oscillator (OSC) is a high-speed clock with a 70-nanosecond period (14.31818 MHz). This signal is not synchronous with the system clock. It has a 50% duty cycle.

#### REFRESH# (I/O)

The REFRESH# signal is used to indicate a refresh cycle and can be driven by a microprocessor on the I/O channel.

#### RESDRV (O)

Reset Drive (RESDRV) is used to reset or initialize system logic at power-up time or during a low line-voltage outage. This signal is active high.

#### SA[19::0] (I/O)

Address bits SA[19::0] are used to address memory and I/O devices within the system. These twenty address lines, in addition to LA[23::17], allow access of up to 16MB of memory. SA[19::0] are gated on the system bus when BALE is high and are latched on the falling edge of BALE. These signals are generated by the microprocessor or DMA Controller. They also may be driven by other microprocessors or DMA controllers that reside on the I/O channel.

#### SBHE# (I/O)

System Bus High Enable (SBHE#) indicates a transfer of data on the upper byte of the data bus, D[15::8]. 16-bit devices use SBHE# to condition data bus buffers tied to D[15::8].

#### SMRDC# (O), MRDC# (I/O)

These signals instruct the memory devices to drive data onto the data bus. SMRDC# is active only when the memory decode is within the low 1MB of memory space. MRDC# is active on all memory read cycles. MRDC# may be driven by any microprocessor or DMA controller in the system. SMRDC is derived from MRDC# and the decode of the low 1MB of memory. When a microprocessor on the I/O channel wishes to drive MRDC#, it must have the address lines valid on the bus for one system clock period before driving MRDC# active. Both signals are active low.

### SMWTC# (O), MWTC# (I/O)

These signals instruct the memory devices to store the data present on the data bus. SMWTC# is active only when the memory decode is within the low 1MB of the memory space. MWTC# is active on all memory write cycles. MWTC# may be driven by any microprocessor or DMA controller in the system. SMWTC# is derived from MWTC# and the decode of the low 1MB of memory. When a microprocessor on the I/O channel wishes to drive MWTC#, it must have the address lines valid on the bus for one system clock period before driving MWTC# active. Both signals are active low.

# T-C (O)

Terminal Count (T-C) provides a pulse when the terminal count for any DMA channel is reached.

# I/O ADDRESS MAP\*

| Hex Range                                                                                                                                              | Device                                                                                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 000-01F<br>020-03F<br>040-05F<br>060-06F<br>070-07F<br>080-09F<br>0A0-0BF<br>0C0-0DF<br>0F0<br>0F1                                                     | DMA Controller 1 Interrupt Controller 1, Master Timer 8042 (Keyboard) Real-time Clock, NMI (non-maskable interrupt) Mask DMA Page Register Interrupt Controller 2 DMA Controller 2 Clear Math Coprocessor Busy Reset Math Coprocessor Math Coprocessor           |