# Taking solution ownership across the value chain

We focus on building long-term partnerships with our clients. We help them meet their current design requirements, develop new strategies for product development, and prepare detailed, derivative roadmaps for future design trends. Backed by our focus on engineering excellence, our solutions for the semiconductor industry and electronics systems industry can help:

- Reduce time-to-market

- Reduce R&D and increase gross margins

- · Build customized solutions

- Offer flexible engagement models

- Improve access to emerging markets

- Provide better standardization

- Mitigate risk and streamline processes

- Increase capacity flexibility

# Case Study

# How Cyient helped streamline a complex physical design for a large networking chip

Developing the physical design of a silicon can be a daunting task. When our client, a leading semiconductor company, requested assistance with the complicated physical design of a large networking chip, we implemented a robust solution designed to deliver 114+ watts of power through multiple functions on the chip.

**Challenge.** The design was based on a TSMC 28 nm HPC technology with 7+2+1 layer stack, which included more than 130 million logic gates, 47 MB SRAM memory, 3 MB-TCAM, 700 MHz IBU, physical coding sublayer IP with 100 G, 40 G, 10 G, a SerDes with 450 MHz frequency, dual core ARM cortex R5 with 500 MHz clock, and power consumption of over 114 watts. This chip also had close to 600 IOs.

**Solution.** Working closely with the customer to understand the unique challenges, we developed custom scripts to handle congested and time-critical blocks. We also employed a semi-custom approach to manage the entire physical design and closure of the high-speed logic.

**Benefit.** By leveraging our domain knowledge in SOC Encounter, Primetime, Conformal, Tweaker, Redhawk, Calibre, and Apache, we were able to seamlessly exceed client expectations. We not only completed this project within the given timeframe, but we also developed a die size of 451 mm², meeting all stringent IR drop requirements.

# **About Cyient**

Cyient (Estd: 1991, NSE: CYIENT) provides engineering, manufacturing, geospatial, network, and operations management services to global industry leaders. We leverage the power of digital technology and advanced analytics capabilities, along with domain knowledge and technical expertise, to solve complex business problems. As a Design, Build and Maintain partner, we take solution ownership across the value chain to help our clients focus on their core, innovate, and stay ahead of the curve.

Relationships lie at the heart of how we work. With nearly 14,000 employees in 21 countries, we partner with clients to operate as part of their extended team, in ways that best suit their organization's culture and requirements. Our industry focus spans aerospace and defense, medical, telecommunications, rail transportation, semiconductor, utilities, industrial, energy, and natural resources.

For more information, please visit www.cyient.com

## Contact Us

## North America Headquarters

Cyient, Inc.

99 East River Drive

5th Floor

East Hartford, CT 06108

T: +1 860 528 5430 F: +1 860 528 5873

## Europe, Middle East, and Africa Headquarters

Cyient Europe Ltd.

High Holborn House 52-54 High Holborn

London WC1V 6RL

JK

T: +44 20 7404 0640

F: +44 20 7404 0664

## Asia Pacific Headquarters

Cyient Limited

Level 1, 350 Collins Street Melbourne, Victoria, 3000

Australia

T: +61 3 8605 4815

F: +61 3 8601 1180

#### Global Headquarters

Cyient Limited Plot No. 11

Software Units Layout Infocity, Madhapur

Hyderabad - 500081

T: +91 40 6764 1000 F: +91 40 2311 0352

© 2017 Cyient. Cyient believes the information in this publication is accurate as of its publication date; such information is subject to change without notice. Cyient acknowledges the proprietary rights of the trademarks and product names of other companies mentioned in this document.

SEM\_BR\_DNV\_OV\_1117

It takes great ingenuity to stay ahead in the competitive and technology-intensive electronics industry. With the idea of 'smart living' at the core of every new product, it is imperative for global leaders to invest in processes and technologies to maintain the competitive edge and improve the bottom-line. Agile businesses are partnering with specialists to complement their research and development (R&D) initiatives and increase return on investment on existing products through the introduction of value engineering.

Cyient offers end-to-end services in the semiconductor and embedded software solutions space with flexible engagement models, helping you identify areas for improvement across the design and manufacturing value chain. We also work closely with your R&D teams to develop custom strategies and offer complete project life cycle management capabilities.

Leveraging our 20+ years of deep domain experience and technical expertise has enabled us to be the design, build, and maintain partner for three of the five leading semiconductor manufacturers. Our problemsolving approach, focus on meeting business objectives, and complete solution ownership ensures that we create real, tangible value to meet your business goals. Our expertise ranges from building concepts to complete products, low power to high power, small to big designs with applications across automotive, consumer, industrial and more!

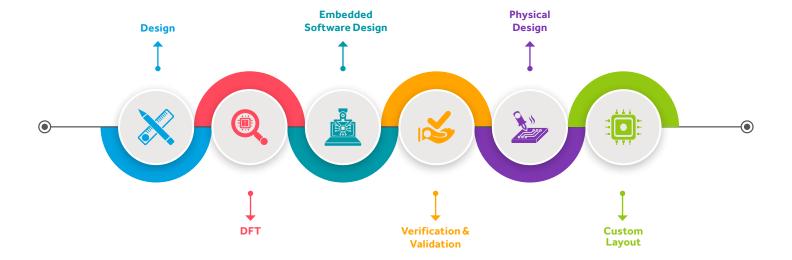

# Our end-to-end design flow capabilities include:

# esign

- Analog, digital, and mixed-signal design experience up to 7 nm

- SoC design expertise with ARM Cortex processors for multiple applications

- VHDL, Verilog, and System Verilog expertise

- Altera, Xilinx, Microsemi FPGA to ASIC flow; full, custom silicon development, feature updates, and process node migration

- Strong relationship with ecosystem players, design tools, EDA tools, and foundries

- Analog and digital IP design, from high power to low power and high speed to low speed

## FT

- Optimal compression techniques with modular approach

- Built-in self-test (memory and logic) and on-chip test resources

- Mixed-signal IP tests with P1500

- Highest test coverage with efficient fault models (transition, path delay, SDD, cell-aware)

- Low-power DFT implementations

- IEEE 1149.1 and 1149.6 standards and performance tests

- Post-silicon ATE support

# Embedded Software Design

- Automotive ADAS and infotainment application development

- Computer vision, handheld application solutions and services

- Industry-experienced embedded software team

- Experience from board support package to system validation

- OS enablement and porting (RTOS, Android, and Linux)

- Third-party IP, application integration

- Testing and validation using LabView, Test Complete, Matlab and Open Source, C, Jscript, Python, and TCL

## Physical Design

- Expertise in floor planning, place and route, timing closure, and timing and IR drop analysis

- Timing closure challenges in advanced technology nodes

- High-performance design of high-frequency clock with hybrid structure

- Automated in-house PD methodology to execute Netlist to GDSII and checklist generation

- $\bullet \ \ Integrated full-chip flow and physical verification \\$

- Expertise in low-power optimization flow, with multi-power domains

- Achieved targets of 6% dynamic and 3% static

IR drop for complex network chip with high-power consumption

## Verification & Validation

- Mixed Signal Verification using advanced OVM & UVM methodologies

- Identification of test cases from the spec, parametric, functional, use cases, DFT, RC extraction, and standard tests with coverage metrics

- Automation, checkers, and regression of test suites to track design changes

- Close-knit process with design and systems functions for first-pass silicon

- Verification expertise: gate-level simulations with SDF annotation, peripherals, assertion-based using SVA, IP, ARM sub-system, and SOC-level

### **Custom Layout**

- Challenging IP development using advanced process nodes 16 nm, 10 nm, and 7 nm

- Layout expertise in both digital and analog domains (ADC, charge pump, linear-switching regulators, SERDES)

- Proprietary methodology to reduce time-to-market

- ESD and bond pad layout design

- Chip-level integration

- RF custom layout capabilities (high-frequency up to 56 GHz)

- Custom memory development: SRAM, ROM